FORD

# CB2 Z-80 CPU Board S-100 Bus

Instruction Manual

# CB2<sup>TM</sup> Z-80 CPU BOARD S-100 Bus

INSTRUCTION MANUAL

SSM MICROCOMPUTER PRODUCTS, INC. 2190 Paragon Drive San Jose, CA 95131

(408) 946-7400 TWX: 910-338-2077 Telex: 171171

DDD: (408) 946-3644 (110 Baud)

$^{\text{TM}}\text{CB2}$  is a trademark of SSM Microcomputer Products, Inc.

# TABLE OF CONTENTS

- 1.0 INTRODUCTION

- 2.0 ASSEMBLY INSTRUCTIONS

- 3.0 FUNCTIONAL CHECK

- 4.0 SET-UP

- 4.1 Jumper Options

- 4.1.1 Hold Acknowledge Option (PHLDA)

- 4.1.2 Clock Option  $(\overline{CLK})$

- 4.1.3 Fixed CPU Wait State Option

- 4.1.4 Power-On/Reset Vector Jump Option

- 4.1.5 I/O Address Multiplexing Option

- 4.1.6 Power-On Reset Option

- 4.1.7 Dynamic Memory Refresh Option

- 4.1.8 Spare Buffer

- 4.1.9 Front Panel Sense Switch Option

- 4.1.10 Non-Maskable Interrupt Option

- 4.1.11 MWRITE Option

- 4.1.12 RUN and SINGLE-STEP Options

- 4.1.13 Spare Tri-State Buffer

- 4.1.14 2/4 MHz Clock Flag Option

- 4.1.15 Ø1 STVAL STROBE Option

- 4.2 Switch Settings

- 4.2.1 RUN/STOP and SINGLE-STEP

- 4.2.2 On-Board Memory Addressing

- 4.2.3 On-Board Memory Type Selection

- 4.2.4 CPU Clock Rate Control

- 4.3 Short Form Set-up Worksheet/Record

- 4.4 Header Descriptions

- 5.0 CIRCUIT DESCRIPTIONS

- 5.1 CPU "P" Signals

- 5.1.1 PSYNC

- 5.1.2 PDBIN

- 5.1.3 **PW**R

- 5.1.4 PWAIT

- 5.1.5 PHLDA

- 5.1.6 PSTVAL

- 5.2 CPU Clock Circuits

- 5.2.1 Crystal Oscillator

- 5.2.2 Divide by 4/8 Circuit

- 5.2.3 Ø1/Ø2 Circuit

- 5.2.4 \$1/\$2 Inhibit Circuits

- 5.2.5 CLK

- 5.3 CPU Status (S) Signals

- 5.3.1 SINP

- 5.3.2 **SOUT**

- 5.3.3 SINTA

- 5.3.4 SHLTA

- 5.3.5 SM1

- 5.3.6 SMEMR

- 5.3.7 SWO

- 5.3.8  $4/\overline{2}$  MHz (Special Option)

- 5.4 External Control Signals

- 5.4.1 The RDY Signals

- 5.4.2 PHOLD

- 5.4.3 PINT and PNMI

- 5.4.4 PRESET/POC

- 5.4.5 SINGLE-STEP RUN SSW DSBL

- 5.4.6 (STATUS, ADDR, C/C & DO) DSBL Signals

- 5.5 Address Bus

- 5.6 Data Bus

- 5.7 Extended Address Port

- 5.8 On-Board Memory

- 5.9 Vector Jump

- 6.0 TROUBLESHOOTING HINTS

#### APPENDICES

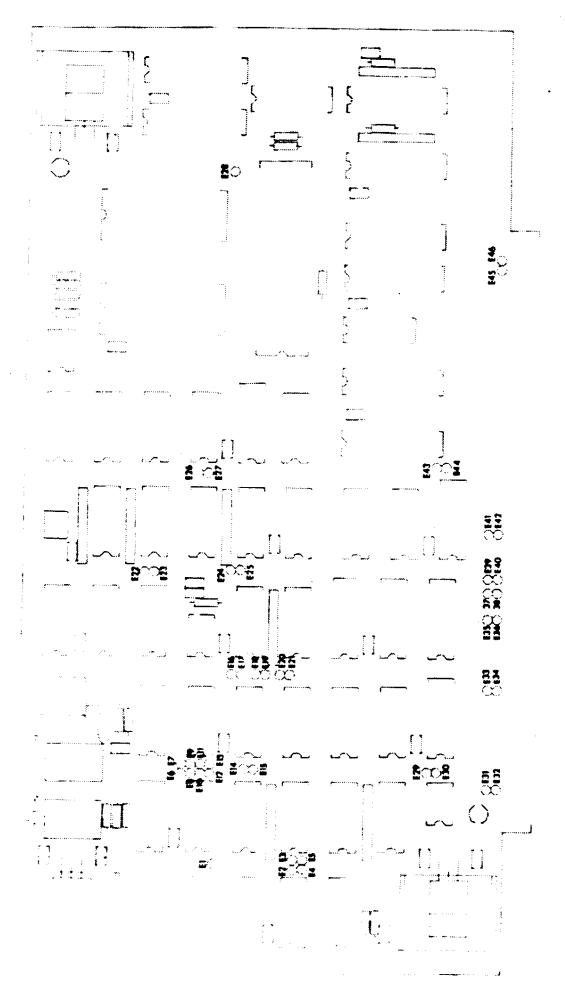

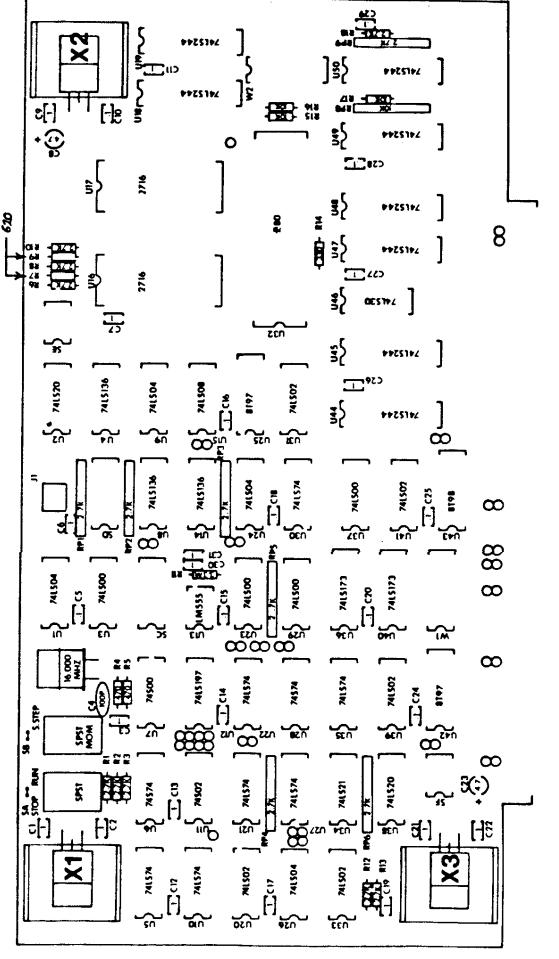

- A-1 ASSEMBLY DRAWING

- A-2 JUMPER DRAWING

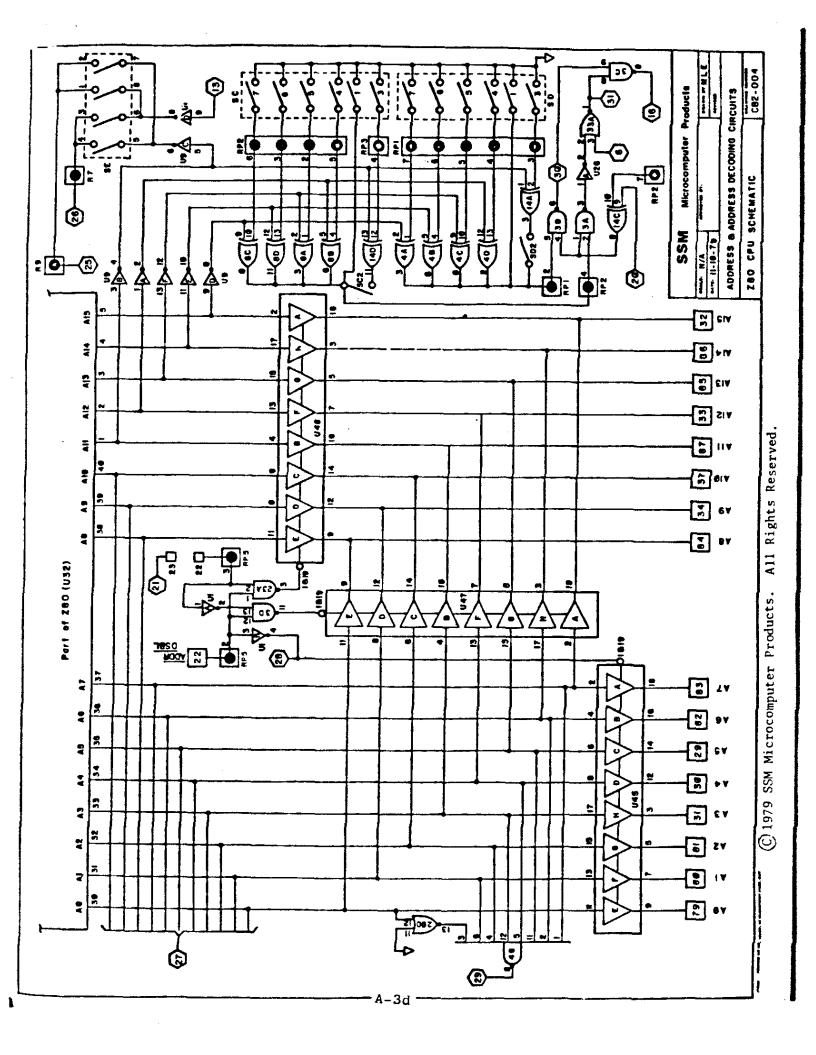

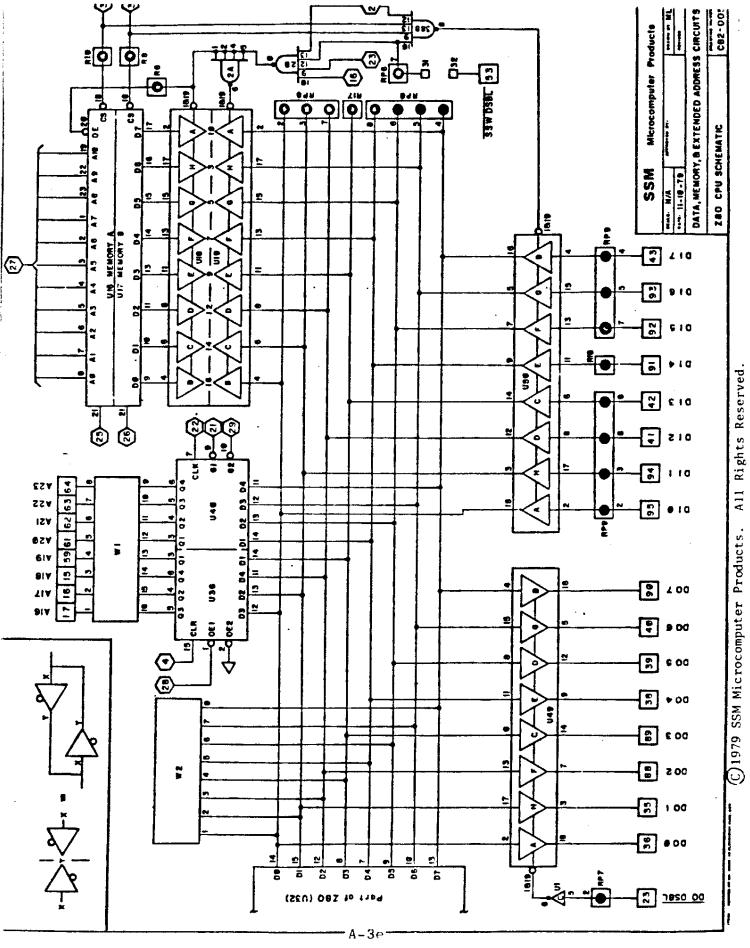

- A-3 CB2 SCHEMATIC INTERPAGE CONNECTION LIST

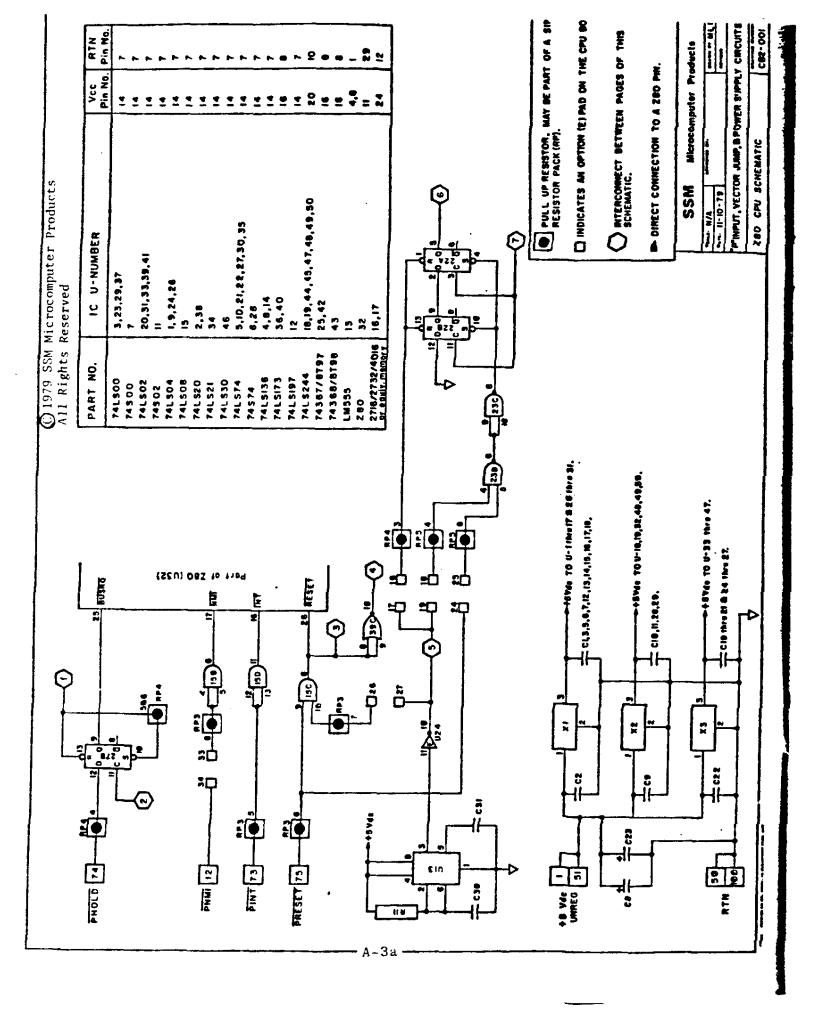

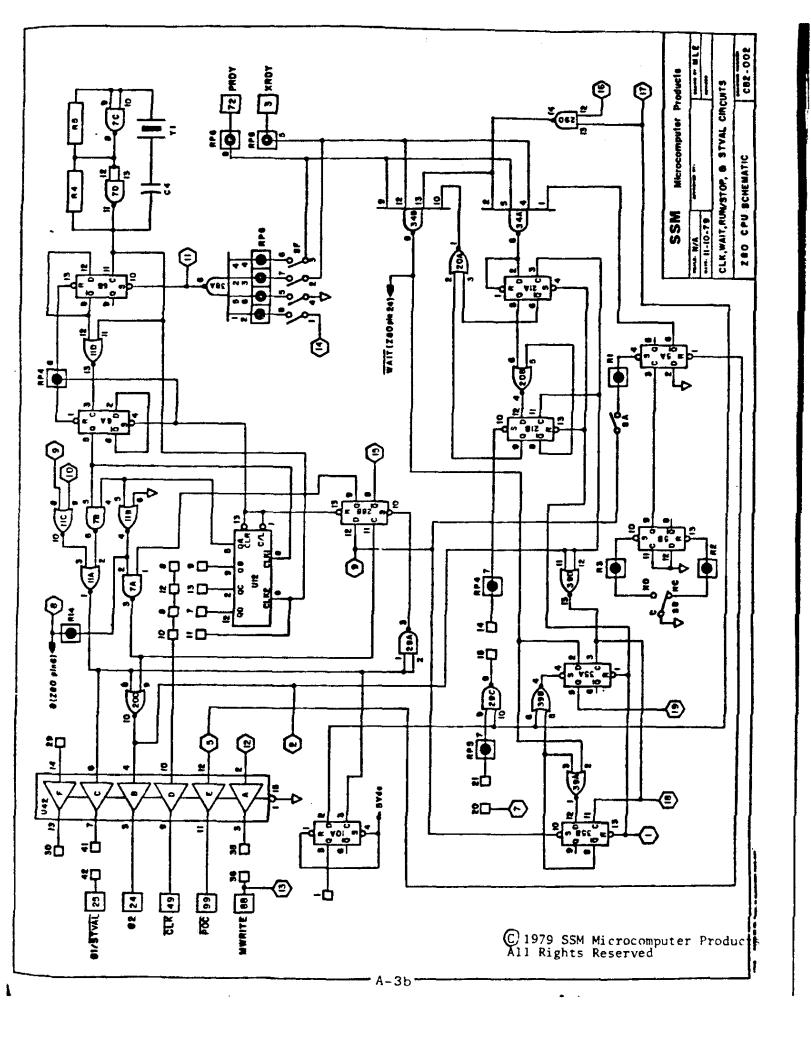

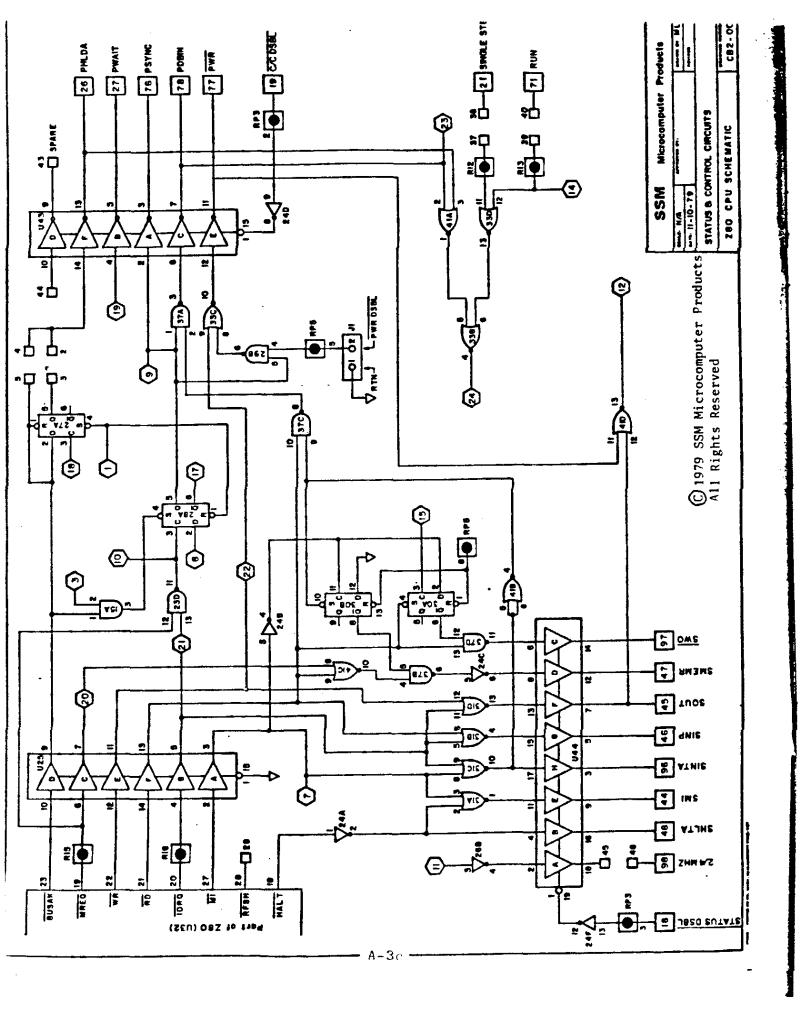

- A-3a SCHEMATIC (5 pages)

- A-4a BUS PIN DEFINITIONS AND CROSS REFERENCE TABLE

- A-5a CB2 PARTS LIST

- A-6a Z-80 TECHNICAL SPECIFICATIONS

- A-7 PRELIMINARY MANUAL REGISTRATION FORM

© 1979 SSM Microcomputer Products All Rights Reserved

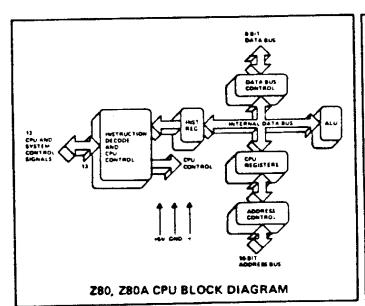

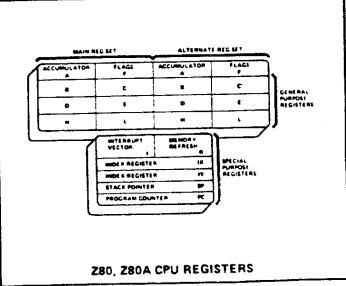

#### 1.0 INTRODUCTION

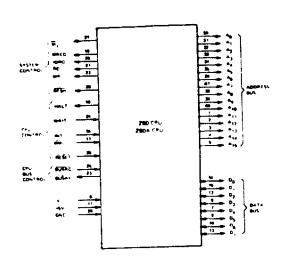

The CB2 is a CPU board, based on the powerful Z-80 micro-processor, for the S-100 computer bus structure. The CB2 is designed to implement as many of the S-100 signals as possible, with the exception of the following: Stack, Interrupt Enable, and CPU status on the data bus during PSYNC.

The CB2 provides the following user-selectable options through on-board switches and wire-wrap jumpers:

- 2 or 4 MHz CPU clock.

- 2/4 MHz clock under XRDY/PRDY/RUN control signals.

- Two on-board sockets for 2716's, 2732's and/or 4016's, with independent addressing for each socket.

- One wait state on each M1 cycle or on each PSYNC.

- On-board MWRITE generation.

- Emulate 8080 I/O addressing.

- Firmware vector jump on power-up/reset.

- On-board RUN/STOP and SINGLE-STEP switches.

- Eight lines of extended addressing or an 8-bit output port.

- Phase One or STVAL\* signals available.

- NMI and Refresh signals available.

The PSYNC/Ø1/Ø2 signals are probably the most critical and difficult to generate on a Z-80 based S-100 CPU board. These signals are used by many of the other S-100 boards you may want to use and therefore must maintain the correct timing relationship between themselves and other S-100 signals. Considerable design effort went into the generation of these signals by the CB2 in order to guarantee its operation with the majority of the S-100 boards being manufactured. To obtain a more detailed description of these and the other S-100 signals, see the theory of operation section of this manual.

Many users may have heard of the proposed new IEEE 696.1 bus standard. The CB2 is designed to conform to this new

<sup>\*</sup> STVAL is a new IEEE 696.1 bus signal.

standard as much as possible and yet remain compatible with the old S-100 standard. The new IEEE standard eliminates many of the old S-100 signals that are needed by many of the systems with front panels. The CB2 is compatible with the old standard and with systems that have front panels, while maintaining the ability to be converted over to the new IEEE standard in the future. Details of this optional capability and other user-selectable options are described in the set-up section of this manual.

# 2.0 ASSEMBLY INSTRUCTIONS (refer to Assembly Drawing)

- Check PC board for possible warpage and straighten if required. To straighten the board, bend with the hands (not a vise) against the warp. Sight down the edge of the board after bending to check if the warp was removed; if not, try bending again.

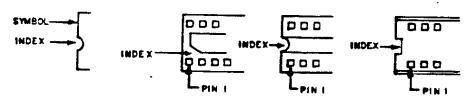

- // Insert the sockets into the component side of the board with the "pin 1" index as indicated in the Assembly Drawing. (The component side is the side on which SSM ©1979 is printed.)

- One (1) 8-pin socket at Location U13

- Thirty-three (33) 14-pin sockets at U1-12,14,15, 20-24,26-31, 33-35,37-39,41,46

- Seven (7) 16-pin sockets at U25,36,40,42,43, W1 & W2

- Eight (8) 20-pin sockets at U18,19,44,45,

- Two (2) 24-pin sockets at U16,17

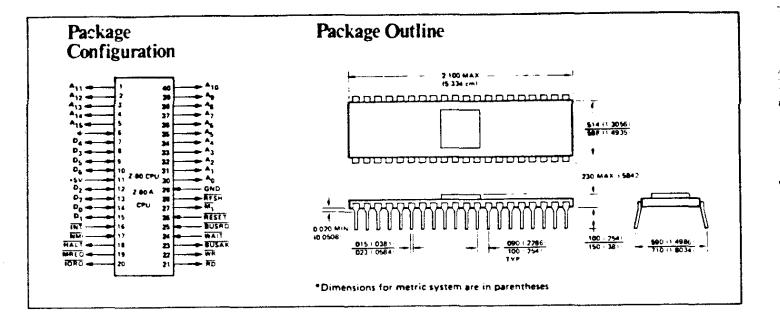

- One (1) 40-pin socket at U32

# Example sockets:

- / Place a flat piece of stiff cardboard of appropriate size on top of the board to hold them in place.

- // Holding the cardboard in place against the sockets, turn the board over and lay it on a flat surface. (Be sure that all of the socket pins are through the holes.)

- // NOTE: Keep soldering iron tip clean to prevent rosin and sludge from being deposited on traces. Wipe tip frequently on a damp cloth, damp sponge or steel wool.

- On each socket, solder two of the corner pins, choosing two that are diagonally opposite of each other.

- 17 Once the sockets are secured, lift the board and check to see if they are flat against the board. If not, seat the sockets by pressing on the top while reheating each soldered pin.

- Complete soldering the remaining pins of each socket.

Touch pin and pad with iron tip, allowing enough solder to flow to form a filet between pin and pad. Keep the tip against the pin and pad just long enough to produce the filet. Too much heat can cause separation of pad and trace from the board. A 600 degree iron is recommended.

- Insert and solder seven 2.7K SIP's (RP1 thru RP6, and RP9). Observe polarity. The end with pin 1 is marked with a dot, notch or bump, and should be installed pointing to the left or upper edge of the PCB.

- $\sqrt{7}$  Insert and solder one 10K SIP (RP8).

- [7] Insert and solder the following resistors:

- 9 2.7K ohm (red, violet, red) at R1 thru R3, R6, R8, R10, R12, R13, and R18.

- 2 620 ohm (blue, red, brown) at R7 and R9.

- 2 470 ohm (yellow, violet, brown) at R4 and R5.

- 1 3.3 Meg ohm (orange, orange, green) at R11.

- 1 330 ohm (orange, orange, brown) at R14.

- 3 10K ohm (brown, black, orange) at R15 thru R17.

- /7 Insert and solder the following capacitors:

- 28 0.1 uf at C1 thru C3, C5 thru C7, C9 thru C22, and C24 thru C31.

- 1 100 pf at C4.

- 2 4.7 uf at C8 and C23 (observe polarity).

- Insert and solder the 16 MHz crystal (Y1). Two holes have been provided on either side of the crystal to solder a strap over the crystal to hold it down.

- Insert and solder the following Dip switches with the numbers right side up (position 1 to the left; position 4 or 7 to the right).

- 2 4 position switches at SE and SF.

- 2 7 position switches at SC and SD.

- // Insert and solder a large momentary two position toggle switch (red handle/with spring return) at SB (right of SA at the top of the board). NOTE: The toggle lever should spring back when pushed.

- // Insert and solder a large two position toggle switch (red handle/non-spring return) at SA (left side at the top of the board).

- Install and solder a two pin right angle molex connector at the top of the board (J1).

- Cut, install and solder 46 header pins. To cut the pins off, place the header strip on its side on some wood and press down on the indentation with a sharp blade (X-acto blade). BE CAREFUL. THE PARTS WILL COME APART WITH ENOUGH FORCE TO SHOOT OFF THE WORKBENCH.

- 2 4 pin headers (E6 thru E13)

- 18 2 pin headers (E2-E5, E14-E27, E29-E46)

- 2 1 pin headers (E1, E28)

- // Place regulators on the board so that the mounting hole in the regulator is in line with the hole in the board. Mark leads for proper bending to match the board holes (allow for a bend radius).

- $/\overline{/}$  Bend regulator leads to match holes in board.

- // If available, apply thermal compound to the back side of each regulator case (the side that will contact the heat sink). Use just a little thermal compound. Too much is worse than none at all.

- // Next, position heatsink and insert regulator IC for each of the 3 regulators (X1, X2 & X3). Finally, position the nut and lockwasher on top of regulator and secure from behind with screw in each case. Be sure regulators and heatsinks fit flat on board and then solder all regulator leads.

- /7 Do not install any IC's at this time.

#### 3.0 FUNCTIONAL CHECK

WARNING! DO NOT INSTALL OR REMOVE BOARD WITH POWER ON. DAMAGE TO THIS AND OTHER BOARDS COULD OCCUR.

This functional check does not examine or verify every signal or feature of the CB2, but does verify proper operation of the on-board regulators, the clock, RUN/STOP and SINGLE STEP circuits.

- 3.1 If an ohmmeter is available, measure the resistance between pin 50 (-) and pin 1 (+) on the edge connector and verify resistance of 20 ohms or greater. If your reading is below 20 ohms, check your board for possible shorts.

- 3.2 Apply power (+8v to +10v) to board by plugging into the computer or by connection to a suitable power supply.

Measure the outputs of the +5v regulators.

The voltage should be between +4.8v and +5.2v. If the regulator doesn't meet this test, check the board for shorts or errors.

CAUTION: WHILE IT HAS NEVER HAPPENED TO US, SHORTED REGULATORS HAVE BEEN KNOWN TO EXPLODE WITH POSSIBLE INJURY TO EYES OR HANDS. BETTER SAFE THAN SORRY--KEEP FACE AND HANDS CLEAR OF THE REGULATOR SIDE OF THE BOARD DURING THIS TEST.

- 3.3 Observing polarity, insert the following IC's into their sockets: U6, U7, U11, U12, and U38. Close all the contacts on switch SF.

- 3.4 Reapply power to the CB2 and verify that U32 pin 6 (Z-80 IC socket) is toggling between logic 0 and 1 at 2 MHz. (Be sure SF, position 4 is closed.) This can be done using either an oscilloscope, counter, or logic probe (or even a DVM set to measure volts; the DVM would read approximately +2.5 Vdc).

- 3.5 Next, verify that the 2/4 MHz circuit is operating. Set switch SF, all positions, to the open or OFF position and

verify a logic 0 at U38 pin 6 and U6 pin 8. Then set switch SF, position 4, to closed or ON position (this sets the CB2 to 2 MHz) and verify a logic 1 at U38 pin 6, and that U6 pin 8 is toggling between logic 0 and logic 1.

3.6 If the clock measurements in paragraphs 3.4 and 3.5 were OK, insert the rest of the IC's into their sockets except the Z-80 (U32). Examine the board carefully for any bent IC pins, then reapply power to the board and verify that the three regulators are still working properly.

NOTE: Set SC and SD position 1 to the ON position to disable the on-board EPROM and RAM for testing purposes.

- 3.7 Now turn off the power and insert the Z-80 IC (U32).

- 3.8 For testing purposes, temporarily wire-wrap the following connections (refer to Jumper Drawing):

| Connection                                         | Comment                                                                                          |

|----------------------------------------------------|--------------------------------------------------------------------------------------------------|

| E6 to E7<br>E16 to E17<br>E22 to E23<br>E26 to E27 | Put 2 MHz on bus pin 49. Disable vector jump circuit. Enable 8080 type of I/O. POC the Z-80 CPU. |

| If you have a S-100 front panel, connect:          | Comment                                                                                          |

| E31 to E32<br>E37 to E38<br>E39 to E40             | Front panel Sense-Switch disable.<br>Front panel SINGLE-STEP signal.<br>Front panel RUN signal.  |

| If you don't have a front panel, connect:          | Comment                                                                                          |

| E35 to E36                                         | Generate MWRITE signal.                                                                          |

- 3.9 Set the RUN/STOP switch (SA) to the stop position (to the left). Verify that U32 pin 24 is at a logic 0, that U28 pin 6 is at a logic 0, and that U25 pin 3 is at a logic 0.

- 3.10 Toggle the SINGLE-STEP switch (SB) and verify that U28 pin 6 toggles once (a pulse).

- 3.11 Set the RUN/STOP switch (SA) back to the right (RUN position) and toggle the SINGLE-STEP switch (SB) once. Verify that U28 pin 6 is pulsing continuously.

- 3.12 Run a small program to output all zeroes to port FE; such as:

AF LOOP: XRA A

D3,FE OUT ØFEH

18,FB JR LOOP

Then verify logic 0's at W1 pins 9 thru 16.

Then, run a similar program to output all 1's to port FE and verify logic 1's at W1 pins 9 thru 16.

#### 4.0 SET-UP

There are a large number of user-selectable options on the CB2 Z-80 CPU board. These options give the user flexibility to configure the board to best meet individual system requirements. The options are selected in one of three ways: (1) by Dip switch, (2) by wire-wrapping, or (3) by header.

# 4.1 Jumper Options

The jumper pads are indicated as E numbers on the jumper drawing and the schematic.

# 4.1.1 Hold Acknowledge Option (PHLDA)

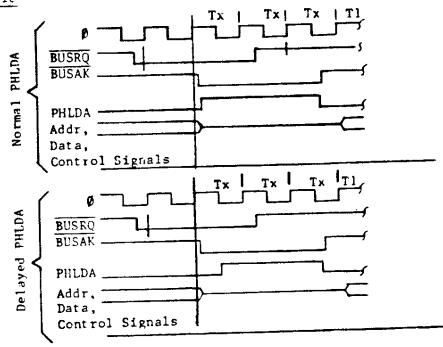

The PHLDA signal can be jumpered to come off the CB2 with the normal Z-80 timing for BUSAK, or it can be jumpered to delay the PHLDA signal turnoff by one-half cycle into the T1 state of the Z-80. The delayed mode guarantees an overlap of the control signals from slave and master during the exchange. See Figure 5.1.5.

|     | $\mathtt{Jumper}$ | Function Selected                                                                                                     |

|-----|-------------------|-----------------------------------------------------------------------------------------------------------------------|

| (a) | E2 to E3          | Delayed turnoff.                                                                                                      |

| (b) | E4 to E5          | Normal Z-80 operation. (If in doubt of which set-up to use, then use the NORMAL MODE until your DMA device is known.) |

# 4.1.2 Clock Option (CLK)

This option allows the user to select either a 2, 4, 8, or 16 MHz clock to come out on the CLK bus line (S-100 pin 49). This clock signal does not change when the CPU is switched between 2 and 4MHz as Phase 1 and Phase 2 do. This clock is not synchronized to the Phase 1 or Phase 2 signals.

|            | Jumper                                           | Function Selected                                         |

|------------|--------------------------------------------------|-----------------------------------------------------------|

| (b)<br>(c) | E6 to E7<br>E8 to E9<br>E10 to E11<br>E12 to E13 | 2 MHz (S-100 & IEEE standard)<br>8 MHz<br>16 MHz<br>4 MHz |

# 4.1.3 Fixed CPU Wait State Option

This option allows the user to select either no extra wait states or one extra wait for M1 (Op-Code Fetch) cycles only, or one extra wait state for all data transfer (Memory and I/O) cycles. The extra wait state for M1 cycles may be necessary with some memory boards because the Z-80 M1 cycle is faster than the 8080 M1 cycle.

|     | Jumper     | Function Selected                       |

|-----|------------|-----------------------------------------|

| (a) | E14 to E15 | Extra wait state for M1 only            |

|     | E20 to E21 |                                         |

| (b) | E14 to E15 | Extra wait state for all data transfers |

| (c) | No jumpers | No extra wait status                    |

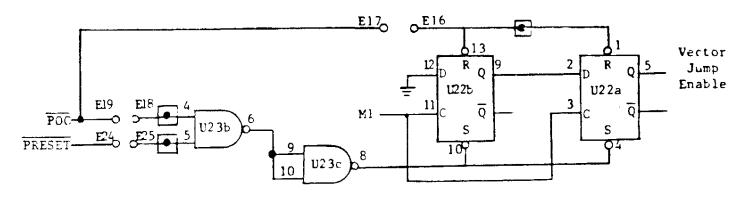

# 4.1.4 Power-On/Reset Vector Jump Option

This option allows the user to execute one instruction at the beginning of ROM A (a ROM must be in the U16 position) like a "jump instruction" after applying power and/or when the CPU receives a reset (from bus pin 75). The CPU is forced to read the first instruction no matter where the ROM is addressed and then reverts back to normal operation.

The first instruction in the user's ROM should be a "jump" to the main entry point of the ROM program which initializes and brings up the computer system.

| Jumper                | Function Selected                  |

|-----------------------|------------------------------------|

| (a) <u>E16 to E17</u> | Vector Jump Disabled               |

| (b) E24 to E25        | Vector Jump on RESET               |

| (c) E18 to E19        | Vector Jump. on POC                |

| (d) E24 to E25<br>and | Vector Jump on either RESET or POC |

| E18 to E19            |                                    |

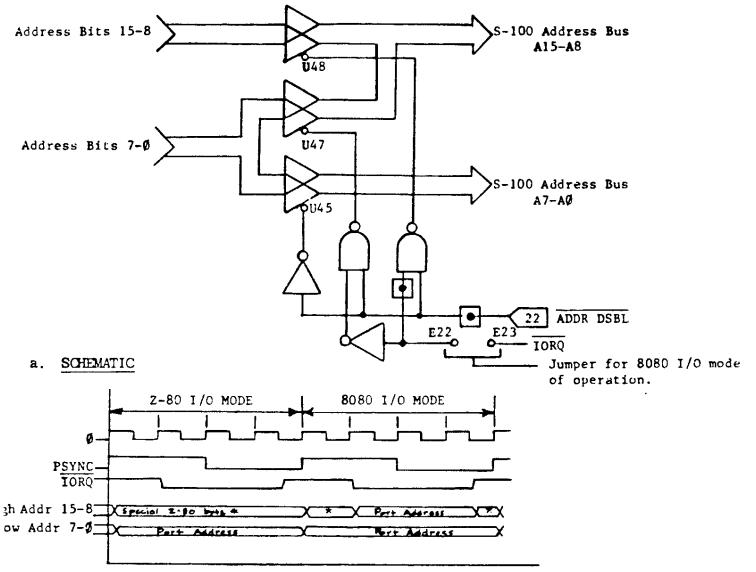

# 4.1.5 I/O Address Multiplexing Option

This option allows the user to multiplex the low order address onto the high order address bus during I/O operations to simulate the way the 8080 CPU operates. The user may or may not want this feature depending on how his I/O cards operate.

The Z-80 CPU puts the accumulator contents on the high order address bus during normal I/O, and the E register (byte counter) is put on the high order address bus during block I/O operations. If the user wants this information to come out on the high address bus, he can disable the multiplexer circuit.

|     | Jumper     | Function Selected                                                       |

|-----|------------|-------------------------------------------------------------------------|

| (a) | E22 to E23 | 8080 configuration (Addr <sub>L</sub> $\rightarrow$ Addr <sub>H</sub> ) |

| (b) | No jumper  | Z-80 configuration                                                      |

# 4.1.6 Power-On Reset Option

The user can prevent  $\overline{POC}$  (pin 99) from resetting the CPU (Z-80) at the application of power to the board. ( $\overline{POC}$  will still occur at pin 99 as usual.)

| Jum            | per Fur    | nction Se | lected    |          |             |

|----------------|------------|-----------|-----------|----------|-------------|

| (a) <u>E26</u> | to E27 PO  | c resets  | Z-80 (mos | t common | connection) |

| (b) No         | jumper POO | ā does no | t reset Z | -80      |             |

# 4.1.7 Dynamic Memory Refresh Option

The Refresh signal is not part of the S-100 standard signals, but it is possible to bring this signal out to one of the S-100 bus lines if it is needed.

|     | Jumper                                                                  | Function Selected                           |

|-----|-------------------------------------------------------------------------|---------------------------------------------|

| (a) | No jumpers                                                              | Refresh not available on S-100 bus          |

| (b) | E28 to E29 and E30 to a solder connection at the top of the desired bus | Buffered Refresh signal to desired bus line |

# 4.1.8 Spare Buffer

A spare buffer is located at U42 which may be used (if not used elsewhere as in 4.1.7 above). This buffer is not tri-stateable (the tri-state control line is always at logic 0). E29 is the buffer input, and E30 is the buffer output.

# 4.1.9 Front Panel Sense Switch Option

finger

The IEEE bus standard deleted this function and put a ground on this line (bus line 53). The old S-100 bus standard used this line in conjunction with front panel operations to disable data from coming in from the bus.

|     | Jumper     | Function Selected       |

|-----|------------|-------------------------|

| (a) | E31 to E32 | SSW enabled (old S-100) |

| (b) | No jumper  | SSW disabled            |

# 4.1.10 Non-Maskable Interrupt Option

The Z-80 microprocessor has a non-maskable interrupt input which the 8080 does not have. Therefore, the original S-100 bus did not have this signal. The IEEE standard has set bus pin 12 for a NMI line.

| Jumper |            | Function Selected          |

|--------|------------|----------------------------|

| (a)    | No jumper  | NMI disabled               |

| (b)    | E33 to E34 | NMI enabled on bus line 12 |

# 4.1.11 MWRITE Option

Systems with front panels have the MWRITE signal generated by the front panel circuit. Therefore, they do not need

this signal from the CPU board. Turnkey systems and other systems without a front panel may need this signal generated by the CPU in order to write into RAM memory.

|     | Jumper     | Function                             |

|-----|------------|--------------------------------------|

| (a) | No jumper  | MWRITE Disabled (front panel system) |

| (b) | E35 to E36 | MWRITE Enabled (no front panel)      |

# 4.1.12 RUN and SINGLE-STEP Options

These are signals on the original S-100 bus to provide front panels with RUN and SINGLE-STEP control lines to the CPU board. These signals are being eliminated in the new IEEE bus standard.

|     | <u>Jumper</u> | Function                           |

|-----|---------------|------------------------------------|

| (a) | E37 to E38    | SINGLE-STEP enabled on bus line 21 |

| (b) | E39 to E40    | RUN signal enabled on bus line 71  |

These signals, when disabled, will default to the normal CPU run mode. The CB2's RUN/STOP and SINGLE-STEP switches will work no matter how E37 thru E40 are connected.

# 4.1.13 Spare Tri-State Buffer

A spare tri-state buffer is located in U43 pins 9 and 10. This buffer is tri-stated by the  $\overline{C/C}$  DSBL control signal on S-100 bus line 19. E44 is the input, and E43 is the output.

# 4.1.14 2/4 MHz Clock Flag Option

In the original S-100 bus, bus line number 98 is the STACK STATUS line. The Z-80 does not produce a STACK status. Therefore, this line was used by \*Cromemco to indicate when the CPU is in 2 or 4 megahertz operation. The CB2 will also indicate 2/4 MHz operation status on this line if E45 and E46 are connected. The new IEEE uses bus line 98 as an error signal line. Therefore, if you are using the IEEE standard, E45 and E46 must not be connected.

<sup>\*</sup> Cromemco, 280 Bernardo Avenue, Mountain View, CA. Manufacturer of Z-80 based products.

|     | Jumper     | Function                              |

|-----|------------|---------------------------------------|

| (a) | No jumper  | 2/4 MHz STATUS disabled               |

| (b) | E45 to E46 | 2/4 MHz STATUS enabled on bus line 98 |

# 4.1.15 Ø1 STVAL STROBE Option

The original S-100 bus has Phase 1 clock on bus line 25. The new IEEE standard has a new signal  $\overline{\text{STVAL}}$  on this line which indicates when the status lines are valid.

| (b) E1 to E44 STVAL on bus line 25 and |     | Jumper     | Function                                          |

|----------------------------------------|-----|------------|---------------------------------------------------|

| E43 to E42                             | ` ' | E1 to E44_ | Phase 1 clock on bus line 25 STVAL on bus line 25 |

# 4.2 Switch Settings

There are six switches/Dip switches on the CB2. The switches are labelled SA through SF on the schematic and assembly drawings. The individual switch positions on the Dip switches are labelled 1, 2, 3, etc. Position 1 is located on the left side of a Dip switch.

# 4.2.1 RUN/STOP and SINGLE-STEP

The two large toggle switches at the upper left side of the CPU board are SA and SB, the RUN/STOP and SINGLE-STEP switches respectively. These switches and their circuitry are provided so the user can stop the processor and single step it if he does not have a front panel. This is a valuable tool when trying to troubleshoot the hardware or software in case of difficulty.

# 4.2.1.1 RUN/STOP (SA)

When thrown to the left, switch SA stops the processor. This allows the user to make logic measurements and to single step the processor with switch SB.

When SA is thrown to the right and SB is toggled, the CPU will go into the run state until SA is again thrown to the left position.

Normally, switch SA will be in the RUN position (to the right), and the processor will come up running when powered up (POC resets the RUN/STOP flip-flop).

# 4.2.1.2 SINGLE-STEP (SB)

This is a spring-loaded momentary switch that will single step the CPU when the RUN/STOP switch (SA) is in the STOP position (to the left). The CPU is single-stepped once each time SB is toggled. SB is used to start the processor when SA is returned to the RUN position (to the right).

# 4.2.2 On-Board Memory Addressing

Dip switches SC and SD provide address selection for memory sockets U16 and U17 respectively.

|                       | FUNCTION                                                                |                                                                         |

|-----------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------|

| Position              | ON/Closed                                                               | OFF/Open                                                                |

| 1*                    | Disable Memory Select 2716/4016**                                       | Enable Memory Select 2732 (A11/Position 3 = don't care)                 |

| 3<br>4<br>5<br>6<br>7 | A11 logic 0<br>A12 logic 0<br>A13 logic 0<br>A14 logic 0<br>A15 logic 0 | All logic 1 |

| Hex                                                          | 1                      | Switch Position        |                      |                      |                      |  |  |

|--------------------------------------------------------------|------------------------|------------------------|----------------------|----------------------|----------------------|--|--|

| Memory Address                                               | 3                      | 4                      | 5                    | <u>6</u>             | 7                    |  |  |

| <b>99</b> 99<br><b>9</b> 899<br><b>19</b> 99<br><b>18</b> 00 | On<br>Off<br>On<br>Off | On<br>On<br>Off<br>Off | On<br>On<br>On<br>On | On<br>On<br>On<br>On | On<br>On<br>On<br>On |  |  |

| •                                                            |                        | :                      |                      |                      |                      |  |  |

| E800<br>F000<br>F800                                         | Off<br>On<br>Off       | On<br>Off<br>Off       | Off<br>Off<br>Off    | Off<br>Off<br>Off    | Off<br>Off<br>Off    |  |  |

<sup>\*</sup> Disable if there is no memory IC in the socket.

\*\* 2716-pin-compatible RAM memory.

# 4.2.3 On-Board Memory Type Selection

Dip switch SE allows the user to select between three types of memory IC's (2716 - 2K EPROM, 2732 - 4K EPROM, and 4016 or equivalent 2K RAM) for each memory socket (U16 and U17).

| Memory               | Socke                  | t U16                  | Socket U17             |                        |  |  |

|----------------------|------------------------|------------------------|------------------------|------------------------|--|--|

| Type                 | Position 1             | Position 2             | Position 3             | Position 4             |  |  |

| 2716<br>2732<br>4016 | Open<br>Open<br>Closed | Open<br>Closed<br>Open | Open<br>Open<br>Closed | Open<br>Closed<br>Open |  |  |

Open = OFF

Closed = ON

(Positions 1 & 3 enable MWRITE to U16 & U17 respectively for RAM memory only.)

(Positions 2 & 4 enable address bit All to U16 & U17 respectively for 2732 - 4K EPROM's only.)

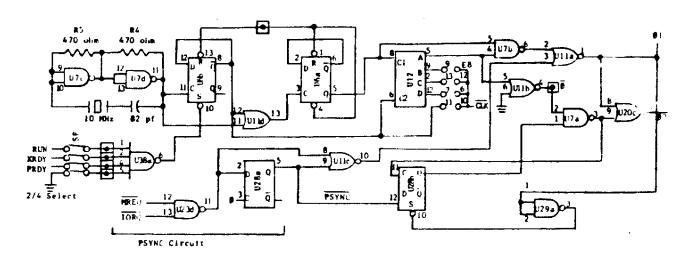

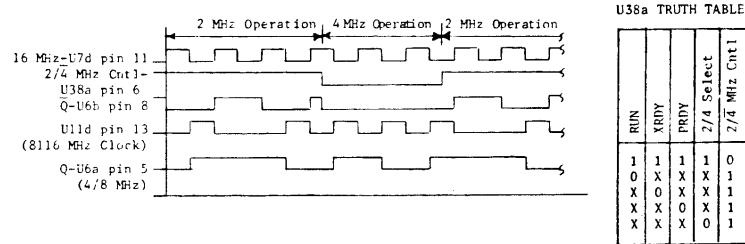

#### 4.2.4 CPU Clock Rate Control

Dip switch SF controls the user-selectable clock rate options. This switch is located at the lower left side of the CPU board.

#### Position Function

- When closed (ON), this switch causes the CPU to go to 2 MHz operation when a front panel stops the computer. This is provided because some front panel circuits cannot operate at 4 MHz. This switch is tied to the S-100 RUN signal on line 71 and will function only if E39 and E40 are jumpered together.

- When closed (ON), this switch allows XRDY (S-100 line 3) to slow the processor to 2 MHz during wait states. Therefore, if the user has slow memory with wait states set for 2 MHZ operation, this will allow him to maintain the same wait time delay.

- Same as Position 2 above, except for PRDY (S-100 line 72).

# Position Function

When closed (ON), this switch selects 2 MHz operation. If this switch position is open (OFF), then 4 MHz is selected.

When all four switches are open (OFF), the CB2 will run at 4 MHz all of the time.

# 4.3 Short Form Setup Worksheet/Record

Due to the large number of options, a short form setup record is provided so the user can record how his board has been set up. This allows you to recall the features and addresses selected at a glance. It also allows you to return the CB2 to its original setup if it is changed temporarily to use it in another system. To use the short form provided, place a check mark in the right-hand box corresponding to the features and switch settings you use. Indicate, with 0's and 1's, the addresses selected for memories in U16 and U17 and write the Hex address in the right-hand box. The numbers on the left are the paragraphs which describe each one.

#### TABLE OF SWITCH SETTINGS REFERENCE PARAGRAPH 4.2.2 ON BOARD MEMORY ADDRESS SETTINGS Switch SC (Address for memory A - IC U16). Switch position 2 3 4 6 Address (A) 12 $\overline{13}$ 14 0 0 0=2716/4016 addressing 1=2732 addressing O=Memory enabled 1=Memory disabled Switch SD (Address for memory B - IC U17). Switch position 5 11 12 13 Address (A) 14 15 \_ 04 0=2716/4016 addressing 1=2732 addressing O=Memory enabled 1=Memory disabled REFERENCE PARAGRAPH ON BOARD MEMORY TYPE SELECTION 4.2.3 Switch SE

| Switch pos | sition       | 1 | 2 | 3 | 4 | ] |

|------------|--------------|---|---|---|---|---|

|            | 2716         | 1 | 1 | - | - |   |

| IC U16     | 2732         | 1 | 0 | - | _ |   |

|            | 4016         | 0 | 1 | _ | - |   |

|            | 2716         | _ | _ | 1 | 1 |   |

| IC U17     | <b>27</b> 32 | - | - | 1 | 0 |   |

|            | 4016         | - | - | 0 | 1 |   |

# TABLE OF SWITCH SETTINGS (continued)

# REFERENCE

# PARAGRAPH 4.2.4 CPU CLOCK RATE CONTROL SETTINGS

# Switch SF

| 2   | MHz | on | RUN      | Pos 1 |   |

|-----|-----|----|----------|-------|---|

|     |     |    | Enabled  | 0     |   |

| Į . |     |    | Disabled | 1     | ¥ |

| 2   | MHz | on | XRDY     | Pos 2 |   |

| l   |     |    | Enabled  | 0     |   |

| l   |     |    | Disabled | 1     | X |

| 2   | MHz | on | PRDY     | Pos 3 |   |

|     |     |    | Enabled  | 0_    |   |

| 1   |     |    | Disabled | 1     |   |

| 2   | MHz | on | l y      | Pos 4 |   |

| 1   |     |    | Enabled  | 0     |   |

| !   |     |    | Disabled | 1     |   |

1=OFF=OPEN

O=ON=CLOSED

-=NOT APPLICABLE

# SHORT FORM SETUP WORKSHEET/RECORD OF JUMPER SELECTIONS

Ref. Para.

| raia.     | <u> </u>                        |                                                  |                                         |                                                    |                                                  |

|-----------|---------------------------------|--------------------------------------------------|-----------------------------------------|----------------------------------------------------|--------------------------------------------------|

| 4.1.1     | PHLDA OPTION                    |                                                  | E2-3                                    | E4-5                                               |                                                  |

|           | Normal Z-80 operation           | <del></del>                                      |                                         | X                                                  |                                                  |

|           | 1/2 cycle turnoff delay         |                                                  | X                                       |                                                    | 1 🗶                                              |

| 4.1.2     | CLK FREQUENCY OPTION            |                                                  |                                         |                                                    |                                                  |

|           | 2 Miz*                          | 1                                                | <u> </u>                                | E6-7                                               | ¥                                                |

|           | 4 MHz                           | <del> </del>                                     |                                         | E12-13                                             | <del>  `-</del>                                  |

|           | 8 MHz                           |                                                  | <b>†</b>                                | E8-9                                               | +                                                |

|           | 16 MHz                          | <del></del>                                      |                                         | E10-11                                             | 1                                                |

| 4.1.3     | WAIT STATE OPTIONS              | <del> </del>                                     | E14-15                                  | E20-21                                             |                                                  |

|           | No added wait states*           | 1                                                |                                         |                                                    | 1                                                |

|           | 1 extra M1 wait state           | <b>-</b>                                         | х                                       | X                                                  | _                                                |

|           | 1 wait state per PSYNC          | 1                                                | X                                       |                                                    |                                                  |

| 4.1.4     | VECTOR JUMP OPTION              | E16-17                                           | <u> </u>                                | E24-25                                             |                                                  |

|           | Vector jump disabled*           | X                                                |                                         | 1                                                  | χ                                                |

|           | Vector jump on RESET            | 1                                                |                                         | X                                                  | <del>                                     </del> |

|           | Vector jump on POC              | 1                                                | Х                                       | <del>†                                      </del> |                                                  |

|           | Vector jump on RESET and POC    | <del> </del>                                     | X                                       | X                                                  | <del> </del>                                     |

| 4.1.5     | I/O ADDRESS OPTION              | 1                                                |                                         | E22-23                                             |                                                  |

|           | 8080 configuration*             | 1                                                | ***                                     | X                                                  |                                                  |

|           | Z-80 configuration              | <del></del>                                      |                                         |                                                    | 7                                                |

| 4.1.6     | POWER-ON RESET OPTION           | 1                                                |                                         | E26-27                                             |                                                  |

|           | POC resets the Z-80*            | 1                                                |                                         | X                                                  | ¥                                                |

|           | POC does not reset the Z-80     |                                                  |                                         | <del>                                     </del>   | 1                                                |

| 4.1.7     | DYNAMIC MEMORY REFRESH (Note 1) | 1                                                | E28-29                                  | E30-( )                                            |                                                  |

|           | Refresh signal on bus line ( )  |                                                  | X                                       | X                                                  |                                                  |

|           | No refresh signal*              | 1                                                |                                         | <del>  ^ -</del>                                   | <del>  </del>                                    |

| 4.1.9     | SSW DSBL OPTION                 |                                                  |                                         | E31-32                                             |                                                  |

|           | Enabled*                        | 1                                                |                                         | X                                                  |                                                  |

|           | Disabled                        | 1 1                                              |                                         |                                                    | 7                                                |

| 4.1.10    | NMI OPTION                      | 1                                                |                                         | E33-34                                             |                                                  |

|           | Enabled                         | 11                                               |                                         | X                                                  |                                                  |

| i         | Disabled*                       | † †                                              |                                         | <u> </u>                                           | 1 -                                              |

| 4.1.11    | MWRITE OPTION                   | 11                                               |                                         | E35-36                                             |                                                  |

|           | Enabled                         | 1 1                                              | · - · · · · · · · · · · · · · · · · · · | X                                                  |                                                  |

| į         | Disabled*                       | † †                                              |                                         |                                                    | +                                                |

| 4.1.12    | RUN/SINGLE-STEP OPTION          | <del> </del>                                     | E37-38                                  | E39-40                                             |                                                  |

|           | Both enabled*                   | 1                                                | X                                       | X                                                  |                                                  |

| t         | SINGLE-STEP enabled only        | <del>                                     </del> | $\frac{\hat{x}}{x}$                     |                                                    | ╀ {                                              |

| t         | RUN enabled only                | <del>1                                    </del> |                                         | X                                                  | 1                                                |

| t         | Both disabled                   | <del> </del>                                     |                                         | <del></del>                                        | +                                                |

| 4.1.14    | 2/4 MHz FLAG OPTION             | <del> </del>                                     |                                         | E45-46                                             |                                                  |

|           | Enabled                         | +                                                |                                         | X                                                  |                                                  |

| <u> </u>  | Disabled*                       | <del>  </del>                                    |                                         | ^                                                  | ╃──┤                                             |

| 4.1.15    | Ø1 STVAL OPTION (Note 1)        | E1-44                                            | E43-42                                  | E41-42                                             |                                                  |

|           | Ø1 on bus line 25*              | 127-44                                           |                                         | X X                                                |                                                  |

| <b> -</b> | STVAL on bus line 25            | X                                                | x                                       | ^                                                  | <del>  </del>                                    |

| L.        | OFFICE OFFICE AND TARE EN       | <u> </u>                                         |                                         |                                                    |                                                  |

<sup>\*</sup> Indicates a standard S-100 set-up.

X Indicates a connection between the indicated E pads.

Note 1: The STVAL and REFRESH signals must be put on the S-100 bus through a tri-state buffer so they can be disabled when necessary. There is only one available tri-stateable buffer (U43). Therefore, only one of these signals can be used.

# 4.4 Header Description

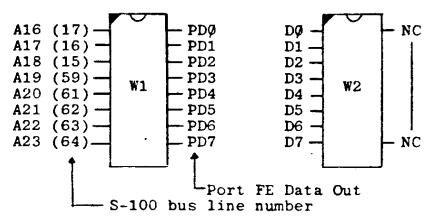

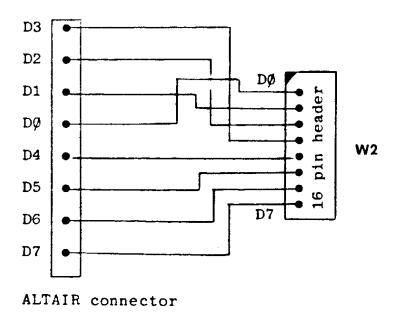

There are two headers (W1 & W2) on the CB2. W1 allows the user to connect port FE to the S-100 bus to be used as extended addressing or to a header with ribbon cable to be used as an output port to an external device. Connecting Pin 1 to Pin 16, Pin 2 to Pin 15, etc., on W1 will provide the user with extended addressing on the S-100 bus through port FE.

W2 is the front panel socket for IMSAI and ALTAIR\* type front panels. W1 and W2 sockets are arranged as follows:

If the user wishes to make an adapter for the CB2 to the ALTAIR connector, it should be connected as follows:

<sup>\*</sup>ALTAIR owners will have to adapt their front panel to CPU board connector to plug into W2.

# 5.0 CIRCUIT DESCRIPTIONS

This section is a short description of the various circuits of the CB2. Some of the circuits described will refer to partial schematics contained within this section, others will refer to the complete CB2 schematics at the back of the manual. The CB2 circuits will be described in the following order: CPU "P" signals, CPU clock circuits, CPU status "S" signals, external control circuits (i.e., RDY, Hold, INT, and Reset), Address Bus circuits, Data Bus circuits, extended address port, on board memory, and vector jump circuit.

# 5.1 <u>CPU "P" Signals</u>

The S-100 "P" signals generated by the CB2 consist of the following signals: PSYNC, PDBIN,  $\overline{PWR}$ , PWAIT, PHLDA, and  $\overline{PSTVAL}$ .

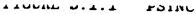

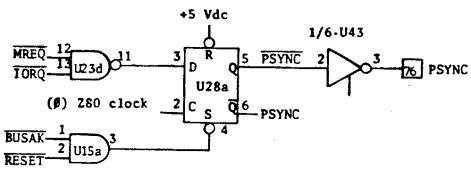

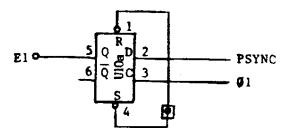

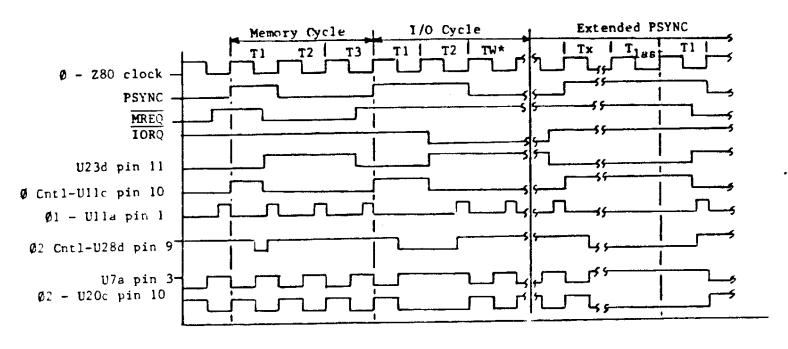

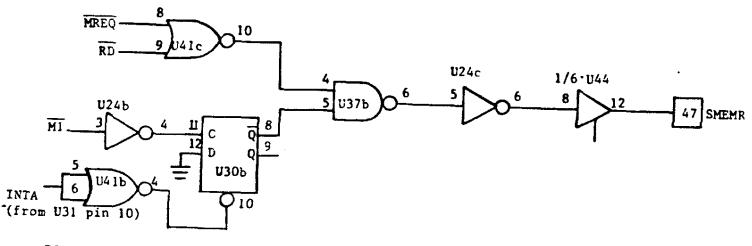

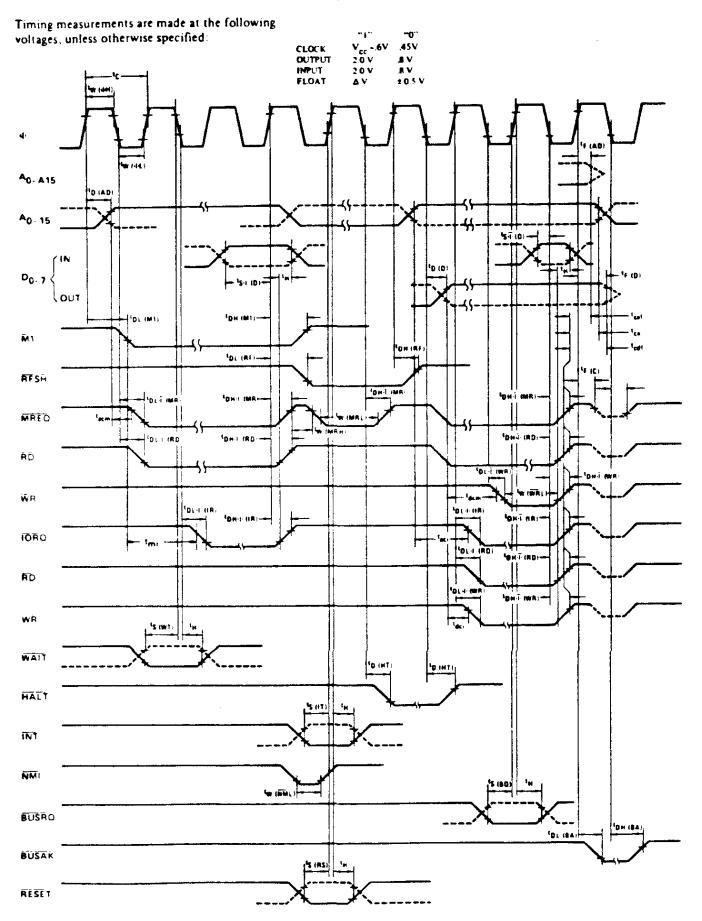

# 5.1.1 PSYNC

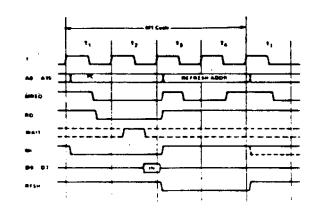

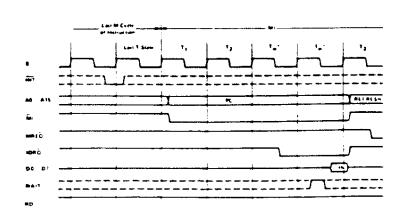

PSYNC is used by many of the S-100 cards and is the only signal on the S-100 bus that indicates the beginning of each byte processed by the CPU board (i.e., memory read or write, I/O read or write, and interrupt acknowledges). The falling edge of PSYNC indicates that the status "S" signals are valid and that the CPU will look for the WAIT (XRDY and PRDY) signals a half cycle later, if wait states are needed. (See Figures 5.1.1a & b).

PSYNC is generated on the CB2 when  $\overline{IORQ}$  and  $\overline{MEMRQ}$  are both at logic 1 on the leading (rising) edge of Phase 2. (See Figures 5.1.1a & b.) Generating PSYNC this way guarantees that the PSYNC signal will go low one-half cycle prior to when the processor expects the first wait request, if needed, which is identical to the 8080 timing for PSYNC and  $\overline{WAIT}$ .

One problem does occur when generating PSYNC this way; some operations cause the PSYNC to exceed one clock cycle in width (as much as 6 cycles). This occurs during I/O operations and when the Z-80 must do internal operations during the M1 machine cycle before proceeding to the next machine operation, such as: index operations, double precision register to register operations, double precision register pushes to the stack, etc. These extra long PSYNC pulses are acceptable to other S-100 boards as long as only one Phase 2 and Phase 1 pulse occurs during PSYNC. The CB2 has circuits to guarantee only one Phase 2 and

# a. SCHEMATIC

# b. TIMING

Phase 1 pulse during PSYNC (see Paragraph 5.2 which describes the clock section).

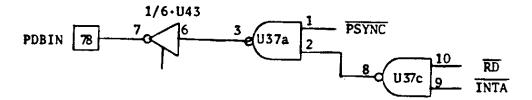

# 5.1.2 PDBIN

This signal is used to gate data onto the Z-80's input when data is to be transferred to the CPU from external devices (such as memory and input ports).

FIGURE 5.1.2 PDBIN

#### a. SCHEMATIC

#### b. PDBIN TIMING

PDBIN occurs during any data transfer into the CPU. The Z-80  $\overline{\text{RD}}$  signal occurs during all memory reads and input operations, but not during interrupt acknowledge. Therefore, this signal is generated when  $\overline{\text{RD}}$  or  $\overline{\text{INTA}}$  occurs (U37 pins 10 & 9). PDBIN in the 8080 does not occur while PSYNC is high; therefore,  $\overline{\text{PSYNC}}$  is used to inhibit PDBIN by U37 pin 1.

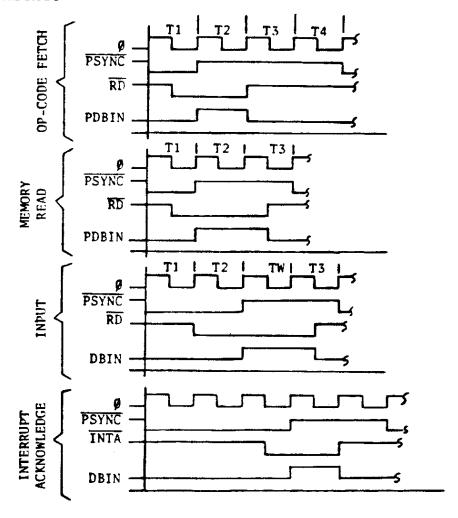

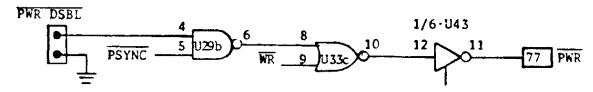

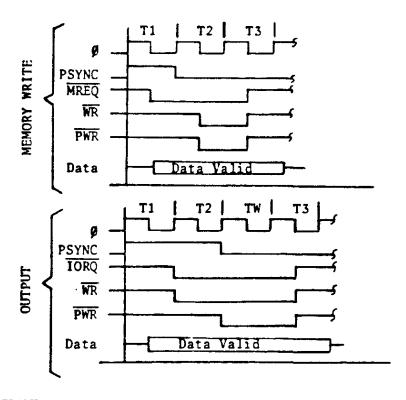

# 5.1.3 PWR

This signal occurs during any memory write or output operation and is used to strobe the data into the memory or output port device.

FIGURE 5.1.3 PWR

#### a. SCHEMATIC

#### b. TIMING DIAGRAMS

The 8080 does not produce  $\overline{WR}$  until after PSYNC; therefore, PSYNC is used to inhibit  $\overline{PWR}$  (U29 pin 5).  $\overline{DWR}$  is a special input at the top of the CB2 card that can be used as an inhibit signal to protect memory from being written into.

# 5.1.4 PWAIT

This signal indicates when the CPU is in a wait state. Some Z-80 CPU cards use XRDY or PRDY as the PWAIT signal on the S-100 bus. This is good for most cases, but some S-100 cards use the PWAIT to generate one wait state by feeding PWAIT inverted to XRDY or PRDY. When this happens, the PWAIT and XRDY or PRDY signals will oscillate. Therefore, the PWAIT signal on the CB2 is synchronized with Phase 2.

FIGURE 5.1.4 PWAIT

#### a. SCHEMATIC

#### b. TIMING DIAGRAM

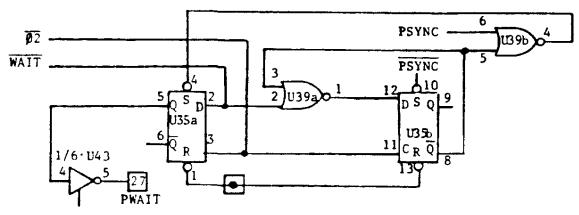

The PWAIT circuit consists of: two flip-flops, U35A & B; two NOR gates, U39B & C; and a tri-state driver, U34B, as shown in Figure 5.1.4. At the beginning of each machine cycle, PSYNC sets both flip-flops. If a WAIT signal is present at the falling edge of \$\pi\_2\$, then U35A changes state to indicate a PWAIT status. The PWAIT status will continue until the WAIT signal is gone at the falling edge of \$\overline{\pi\_2}\$. Since the Z-80 CPU also checks for the WAIT signal on the falling edge of \$\overline{\pi\_2}\$, this circuit reliably indicates when the CPU is waiting.

If a second WAIT signal were applied after the CPU left the WAIT state, the CPU would not accept it until the next machine cycle. Therefore, U35B, and U39B and C are used to inhibit any PWAIT signals after WAIT goes away the first time, or if it is not present on the first falling edge of \$\textit{Q2}\$ after PSYNC. U35B is clocked to the RESET state by \$\textit{Q2}\$ if WAIT is high. Because U35B \$\textit{Q}\$ is now high, U39B & C will always remain low so that U35B cannot change state and U35A is always being set (PWAIT inactive state). This will continue until PSYNC occurs and sets U35B once again.

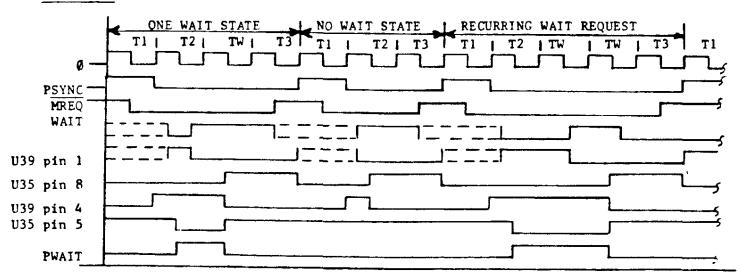

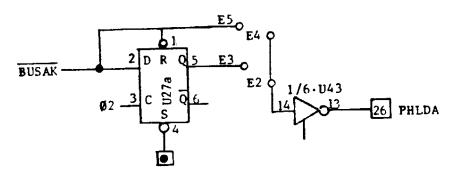

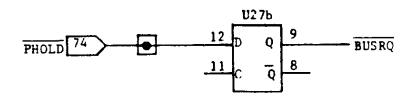

# 5.1.5 PHLDA

This signal indicates to an external device that the CPU is ready to turn over the bus control during a DMA operation. Two methods of asserting and removing PHLDA are provided on the CB2. The first is the Z-80's BUSAK signal inverted, which is found on most CPU cards and is obtained by connecting E4 and E5 together. The second method uses U27 to synchronize PHLDA to Q2. This delays PHLDA slightly, which guarantees that all lines are tri-stated by the CPU when PHLDA is asserted, and that the CPU has reapplied all signals just prior to removing PHLDA. This mode allows a cleaner DMA transfer of control on the S-100 bus. In order to select this method, E4 to E5 must be opened and E2 to E3 must be connected.

# 5.1.6 PSTVAL

This is a new IEEE standard signal and goes low to indicate when status is valid on S-100 bus. This signal goes low at Ø1 during PSYNC and returns to a high state at the next Ø1 clock after PSYNC. This signal is created by clocking PSYNC into U10B by the Ø1 clock.

FIGURE 5.1.5 PHLDA

# a. SCHEMATIC

# b. TIMING DIAGRAM

PSTVAL was allocated to pin 25 on the S-100 bus, which is the Ø1 pin on the old S-100 bus standard. Therefore, the user will have to decide which signal he wants to use. If PSTVAL is desired, then connect E1 to E44 and E42 to E43.

#### FIGURE 5.1,6 PSTVAL

#### a. SCHEMATIC

# b. TIMING DIAGRAM

# 5.2 CPU Clock Circuits

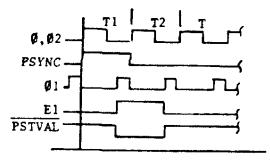

The CB2 clock circuits consist of a crystal oscillator, a selectable divide-by-4/8 circuit, a circuit to generate a non-overlapping 01/02, a circuit to inhibit all but one 01/02 pulse during extended PSYNC's (see Figure 5.1.1), and a selectable fixed clock frequency for the CLK signal on the S-100 bus. The following descriptions will all refer to Figure 5.2.

# 5.2.1 Crystal Oscillator

The oscillator circuit consists of two NAND gates (U7C and U7D) connected to form an oscillator with the 16 MHz crystal as the tuned element. Resistors R4 and R5 are feedback resistors to bias the NAND gates to operate in their linear regions. Capacitor C4 provides a DC voltage block for the crystal, which could be overstressed by a large DC potential. It also provides an extra phase shift to insure reliable operation.

# FIGURE 5.2 CPU CLOCK CIRCUIT (Page 1 of 2)

#### a. SCHEMATIC

# b. $2/\overline{4}$ MHz CIRCUIT TIMING

X=Don't care

# c. 01/02 GENERATION CIRCUIT TIMING

FIGURE 5.2 CPU CLOCK CIRCUIT (Page 2 of 2)

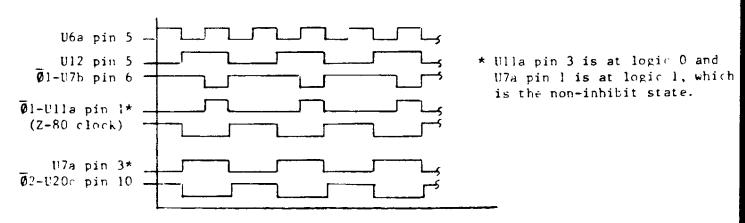

# d. 91/92 INHIBIT CIRCUIT TIMING

# 5.2.2 Divide by 4/8 Circuit

This circuit consists of U6, U7, U11, and U12, which produce the two frequencies necessary to synthesize Ø1 and Ø2 for both 2 and 4 MHz operation.

The flip-flop U6B, when held in the set state by U38A, applies a constant logic 0 to U11D pin 12. The other U11D input (pin 11) is the crystal osciallator's output (16 MHz), which passes straight through U11 and is inverted. This provides the clock to U6A for 4 MHz operation.

When U6B is not held in the set state by U38A (a logic 1 at U6 pin 10), it changes states at half the frequency of the 16 MHz osciallator and inhibits every other clock pulse out of U11. This provides an 8 MHz clock to U6A for a 2 MHz operation of the CB2.

The dividers U6A and U12 divide the output of U11 by 4 to provide the phases necessary to synthesize  $\emptyset$ 1 and  $\emptyset$ 2.

# 5.2.3 <u>\$\phi\_1/\phi\_2\$ Circuit</u>

The  $\emptyset$ 1 circuit consists of U7B and U11A. U7B produces a  $\overline{\emptyset}$ 1 pulse by combining U12-QA (which is  $\overline{\emptyset}$ 2 before it is

processed through the control gates) and U6-Q. The  $\emptyset$ 1 pulse is produced by gating  $\overline{\emptyset}$ 1 through U11A along with the  $\emptyset$ 1 control signal, which is used to inhibit  $\emptyset$ 1 during extended PSYNC's.

The  $\emptyset 2$  circuit consists of U11B, U7A, and U20C. U11B inverts the  $\overline{\emptyset 2}$  signal of U12-QA to produce the Z-80 clock. The Z-80 clock is gated (U7A) by the  $\emptyset 2$  control (which eliminates all but the first  $\emptyset 2$  pulse during extended PSYNC's) to produce  $\overline{\emptyset 2}$ -PRIME.

The  $\overline{\emptyset2}$ -PRIME signal is gated and inverted by U2OC, along with  $\emptyset1$ , to produce a  $\emptyset2$  signal which cannot occur until after  $\emptyset1$  falls. In this way,  $\emptyset1$  and  $\emptyset2$  are guaranteed not to overlap.

# 5.2.4 Ø1/Ø2 Inhibit Circuits

The Ø1 inhibit circuit consists of U11C, which combines PSYNC from U28A pin 5 and (MREQ · IORQ) to produce a logic 1 when both of these signals are a logic 0. When U11C is at a logic 1, Ø1 is inhibited by U11A. This occurs during PYSNC until eihter MREQ or IORQ goes to a logic Ø, which allows Ø1 to occur and then PSYNC falls when Ø2 occurs.

The  $\emptyset 2$  inhibit circuit consists of U28B and U29A. U28B is triggered by Z-80 CLOCK and its D input is PSYNC. Therefore, U28B-Q output is generally a logic 1 until PSYNC occurs. At this time, the Q output of U28B will go low on the rising edge of Z-80 CLOCK. Now  $\emptyset 2$  cannot occur again until  $\overline{\emptyset 1}$  (generated by U29A) occurs. Effectively, all  $\emptyset 2$  clocks during PSYNC are inhibited, except for the first one.

During a normal PSYNC of one clock width, there is no change to 01 and 02. During a stretched PSYNC, there is still only one 01 and 02 pulse, but they may be separated by the equivalent of several clock cycles of time.

# 5.2.5 <u>CLK</u>

In the original S-100 bus, this signal is the same frequency as  $\emptyset 2$  (2 MHz but with the opposite phase). In the new IEEE bus standard, it is still 2 MHz but has no definite phase relationship to  $\emptyset 2$ .

The CB2 CLK circuit consists of part of U12, which divides the 16 MHz clock by 8. The 74197 does this by dividing by 2 three times. The output of each divide-by-2 stage and the 16 MHz clock are available to the user to be used as the CLK signals. This means the user can select either 16, 8, 4, or 2 MHz as CLK.

#### 5.3 CPU Status (S) Signals

In the original S-100 8080 CPU, these signals were taken from the Data Bus during PSYNC, and were then latched onto the S-100 bus through an 8212 or similar tri-stateable latch. The "S" signals indicate the type of data transfer to be performed (i.e., Memory, I/O, or Interrupt Acknowledge), the direction of data transfer (i.e., writing or reading) and the state of the CPU (i.e., Op-Code Fetch, stacking operation, and whether interrupts were enabled).

These signals do not occur on the data bus of the Z-80 as they do in the 8080. They are generated by logically combining the Z-80 control signals. An optional 2/4 MHz status signal is included to indicate when the CB2 is in 2 or 4 MHz mode of operation.

#### 5.3.1 SINP

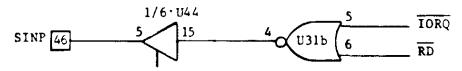

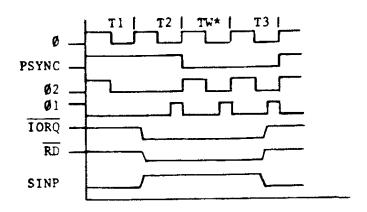

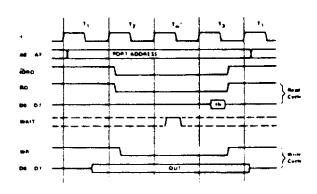

SINP (input) is used to indicate when the CPU is executing an input operation and is used by I/O circuits, along with address, to determine when they are being accessed. SINP is generated by U31B when  $\overline{IORQ}$  and  $\overline{RD}$  are both at logic O. See Figure 5.3.1b for a timing diagram of an input operation.

FIGURE 5.3.1 SINP

#### a. SCHEMATIC

#### b. SINP TIMING

#### 5.3.2 <u>SOUT</u>

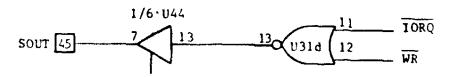

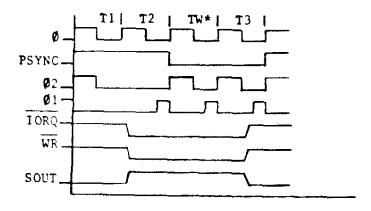

SOUT (output) is used to indicate when the CPU is executing an output operation and is used by I/O circuits, along with address, to determine when they are being accessed. SOUT is generated by U31D when  $\overline{\text{IORQ}}$  and  $\overline{\text{WR}}$  are both at logic 0. See Figure 5.3.2b for a timing diagram of an output operation.

FIGURE 5.3.2 SOUT

#### a. SCHEMATIC

#### b. SOUT TIMING

#### 5.3.3 SINTA

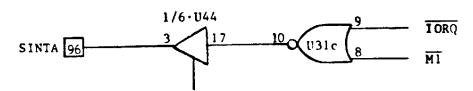

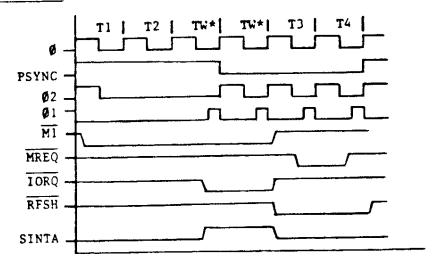

SINTA (interrupt acknowledge) is used to indicate when the CPU is ready to receive a byte from an interrupting device. SINTA is generated by U31C when  $\overline{\text{IORQ}}$  and  $\overline{\text{MI}}$  are both at logic 0. See Figure 5.3.3b for a timing diagram of an interrupt acknowledge operation.

FIGURE 5.3.3 SINTA

#### a. SCHEMATIC

#### b. SINTA TIMING

#### 5.3.4 SHLTA

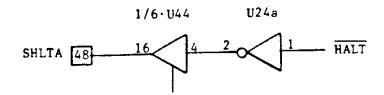

SHLTA (halt acknowledge) is used to indicate when the CPU is in a halted state. A RESET or Interrupt is required to resume operation. SHLTA is generated by inverting the CPU HALT signal through U24A.

FIGURE 5.3.4 SHLTA Schematic

#### 5.3.5 SM1

SM1 indicates, to external devices, when the CPU is in an Op-Code Fetch cycle. This signal is basically the same in 8080 and Z-80 operation, except for when the CPU is in a HALT state. The Z-80 puts out an M1 and the 8080 does not. Therefore, SM1 is the inversion of M1 from the Z-80 and is inhibited by the SHLTA signal.

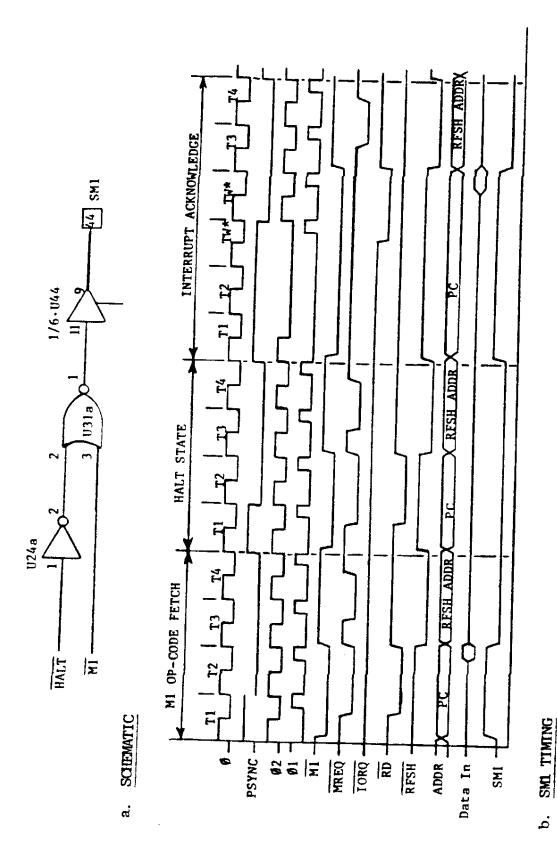

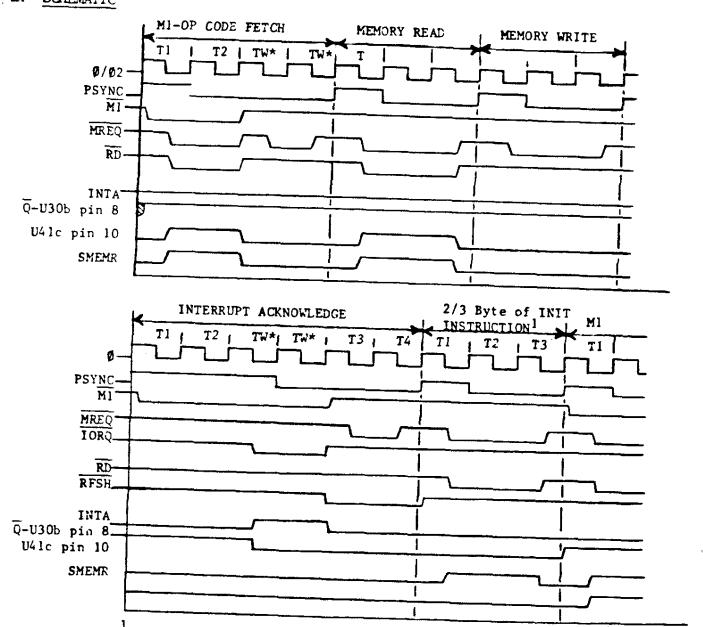

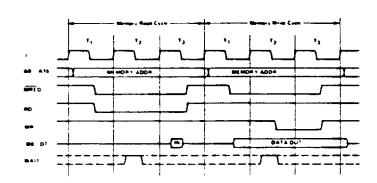

#### 5.3.6 SMEMR

SMEMR (memory read) status indicates to external devices that a memory read operation is taking place.

The SMEMR circuit consists of U418 & C, U30B, U24C, and U37B. U41C puts out a logic 1 when both MREQ and RD are low. This logic 1 passes through U24C/U37B to become SMEMR, unless inhibited by U30B. Normally, U30B's Q output is a logic 1, but an interrupt acknowledge sets U30B, which inhibits SMEMR until the next M1 cycle.

The reason for a SMEMR inhibit circuit on interrupts is because of the way the Z-80 CPU handles status on 2 or 3 byte instructions during an interrupt operation. The 8080 CPU did not turn on SMEMR during an interrupt operation, since it was not a memory operation. The Z-80 will try to indicate SMEMR on the second and third byte of an interrupt operation, which would cause a hardware conflict between the interrupt controller board and a memory board on the S-100 bus. The CB2 is designed to inhibit the SMEMR signal during an interrupt operation until the next SM1 cycle, to prevent bus conflicts.

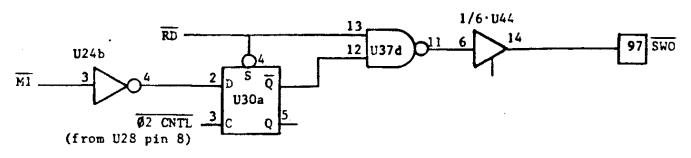

#### 5.3.7 SWO

This signal indicates to external devices when data is being put on the data bus during a memory write or output operation.

The  $\overline{SWO}$  circuit consists of U37D and U30A. The signal  $\overline{WR}$  (from the Z-80) occurs too late in a memory write operation, so  $\overline{RD}$  is used to generate the  $\overline{SWO}$  signal. Therefore, if the CPU is not reading data, then the operation is a data out transfer.

$\overline{\text{SWO}}$  is generated by U37B, which inverts  $\overline{\text{RD}}$ . Because  $\overline{\text{RD}}$  does not remain low during the entire memory read or input operations, U30A is used to inhibit  $\overline{\text{SWO}}$  until the next PSYNC, which does occur on an M1 cycle. In this way,  $\overline{\text{SWO}}$  does not change except under PSYNC, and does occur prior to  $\overline{\text{PWR}}$  as it should.

FIGURE 5.3.5 SM1

#### a. SCHEMATIC

This cycle applies only if the interrupt instruction has an address byte or word (i.e., JMP or CALL).

#### SMEMR TIMING

#### a. SCHEMATIC

#### b. SWO TIMING

#### 5.3.8 $4/\overline{2}$ MHz\* (Special Option)

This signal indicates the CPU clock rate to external devices. U26B inverts the 2/4 MHz control signal from U38A to generate this signal. A logic 1 means the CB2 is operating at 4 MHz, and a logic 0 indicates 2 MHz. Because this is not a standard S-100 signal, it remains for the user to connect it to the bus if desired. Bus pin 98 is STACK on the old S-100; it is 4/2 MHz for Cromemco systems; it is ERROR for the new IEEE standard.

#### 5.4 External Control Signals

These are signals generated by external devices to control the CPU operation. They include XRDY, PRDY, PHOLD, PINT, NMI, PRESET/POC, SINGLE STEP, RUN, SSW DSBL, C/C DSBL, STATUS DSBL, ADDR DSBL, and DO DSBL.

#### 5.4.1 The RDY Signals

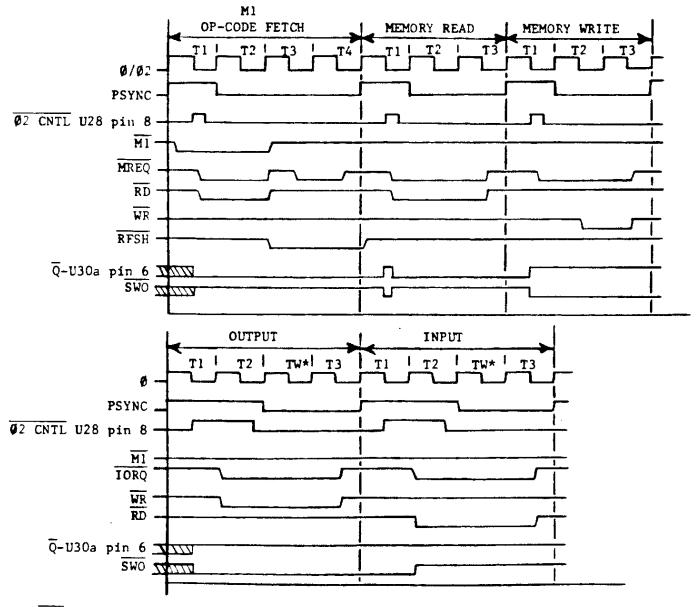

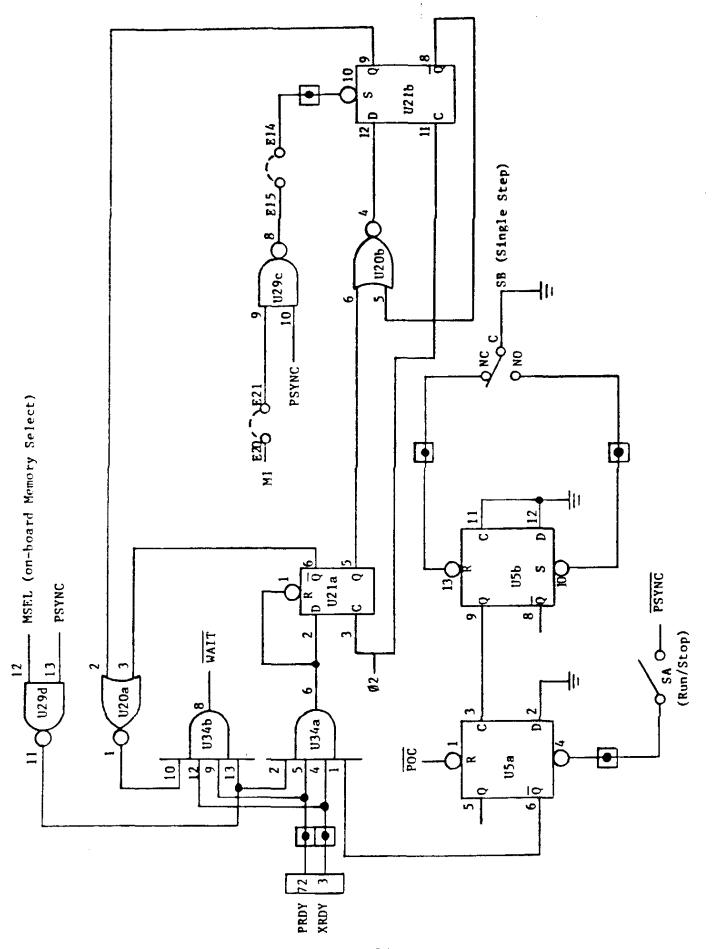

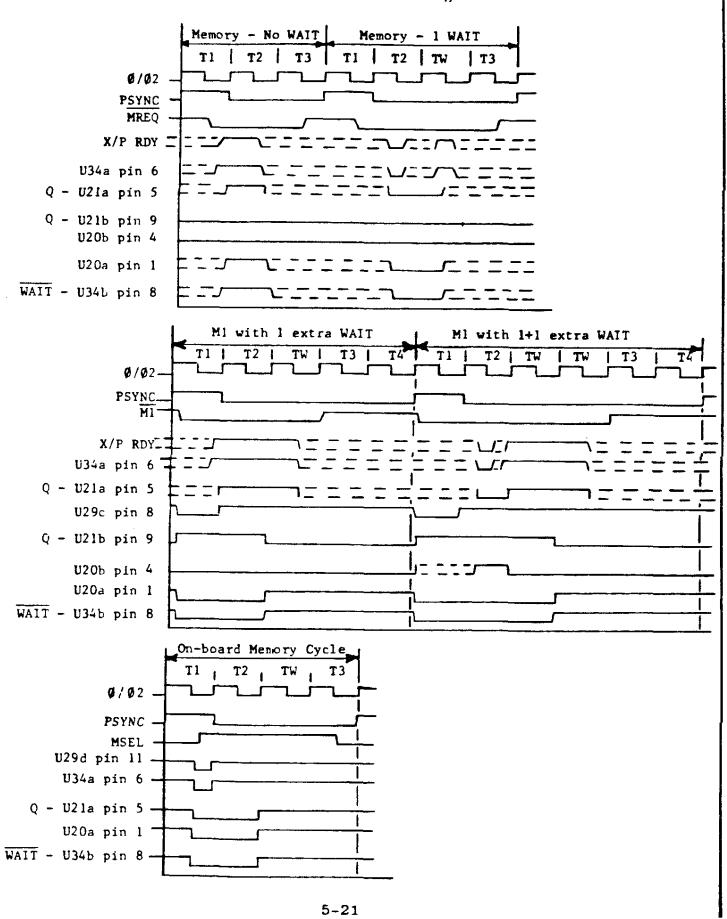

The XRDY and PRDY signals are used to cause the CPU to enter into wait cycles. With these signals, slow memory and I/O devices can slow down the processor to their pace. They also provide a means for a front panel to stop the processor. The on board RUN/STOP and SINGLE-STEP circuits will also be discussed in this section.

#### 5.4.1.1 XRDY and PRDY

The basic XRDY and PRDY circuit is made up of U34A & B, U20A, and U21. The XRDY and PRDY signals go to both the A & B AND gates of U34. U34B immediately sends a logic 0 to the Z-80 WAIT input when either XRDY or PRDY goes low. This allows an external device to request a wait state as late as 90 ns prior to the first falling edge of  $\emptyset 2$  after PSYNC goes low. This is needed because some status signals do not occur until just before PSYNC falls. The output of U34A goes to the reset and D inputs of U21A. This holds U21A reset until XRDY and PRDY are both high, and the next  $\emptyset 2$  pulse strobes a logic 1 in. While reset, U21A  $\overline{\mathbb{Q}}$  is a logic 1 and U20A is a logic 0. Therefore, U34B remains low, holding the CPU in a wait state, and U21A insures that the wait state is removed in sync to  $\emptyset 2$ .

<sup>\*</sup> This signal is similar to the speed flag used by Cromemco.

FIGURE 5.4.1 RDY CIRCUIT

a. Schematic

5-20

FIGURE 5.4.1 RDY CIRCUIT b. XRDY & PRDY Timing

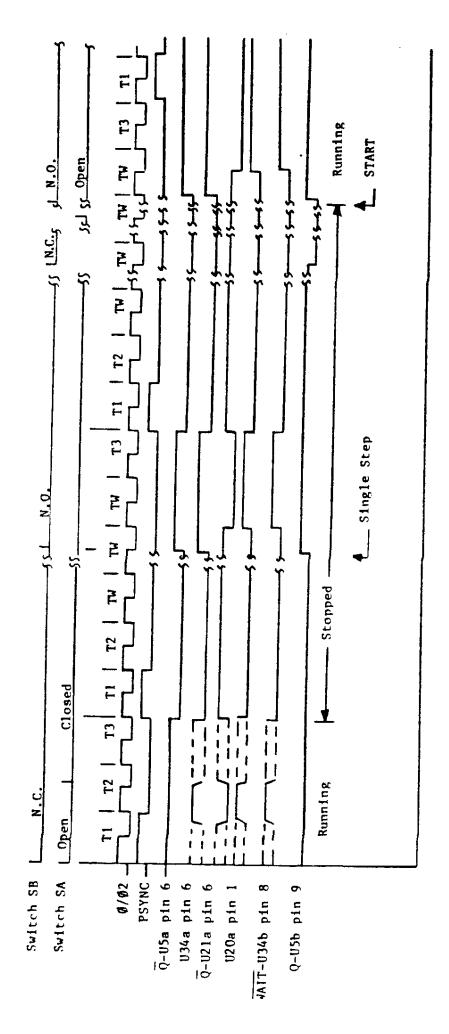

FIGURE 5.4.1 RDY - RUN/STOP - SINGLE-STEP CIRCUIT c. RUN/STOP and SINGLE-STEP Timing

#### 5.4.1.2 On-Board Memory Wait

The on-board memory, when enabled, generates one wait state by gating PSYNC and MADDR (from the memory chip select circuit) through U29D to apply a logic 0 to U34A & B. This logic 0 looks the same as an XRDY or PRDY, and remains low as long as PSYNC is high. Therefore, one wait state is sent to the CPU.

#### 5.4.1.3 Extra M1 Wait State

An extra wait state can be added to each M1 cycle through the circuit of U20A & B, U21B, and U29C. This cirucit was incorporated in the wait circuit because the M1 cycle on the Z-80 is shorter than the other cycles. combines PSYNC and M1 to set U21B, with a logic 1 to U20A. U20A (through U34B) causes a logic 0 to be applied to the CPU WAIT input. If XRDY or PRDY are also requesting a wait state, then U20B will see a logic 0 on both inputs. and a logic 1 is applied to U21B's D input. Therefore, U21B remains set until U21A changes state and then, one cycle later, U21B will be reset. If no XRDY or PRDY wait states are requested, then U21B is reset after one wait state is generated because of U20B applying a logic 0 to U21B's D input. U21B can be set only through its SET input because when it is in the reset state, it applies a logic 1 (U21B  $\overline{Q}$  output) to U20B, and a logic 1 on either of U20B's inputs causes a logic 0 to be applied to U21B's D input.

#### 5.4.1.4 On-Board RUN/STOP and SINGLE-STEP

The on-board RUN/STOP (R/S) and SINGLE-STEP (SS) allow the user to do some limited troubleshooting of the CPU and computer systems without a front panel. The R/S flip-flop U5A is set by PSYNC whenever switch SA is closed. This applies a logic O (U5A-Q) to U34A, which puts the CPU in a wait state. The CPU will remain in a wait state until U5B is reset by a clock pulse from U5A. When clocked by U5A, U5B will release the CPU from the wait state but will again stop the CPU at the next PSYNC if SA remains closed. In this way, the CPU is single-stepped. To restart the CPU, the switch SA is opened and SB is toggled to clock U5B. The flip-flop U5A is used as a switch debouncer.

#### 5.4.2 PHOLD

The  $\overline{PHOLD}$  is applied to U27B, which synchronizes it with  $\emptyset 2$ .  $\overline{PHOLD}$  indicates that another device wishes to gain control of the bus for a DMA (Direct Memory Access) operation.

#### FIGURE 5.4.2 PHOLD

#### 5.4.3 PINT and PNMI

These are interrupt request signals from other devices, and are buffered by U15B & D. PINT will be serviced by the CPU if the interrupts are enabled. PNMI is always serviced since the interrupt enable flag in the CPU has no effect on it.

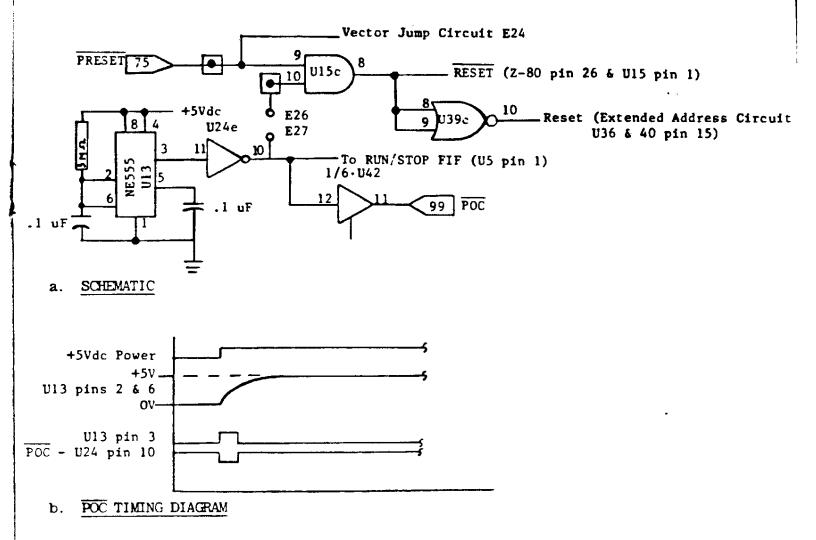

#### 5.4.4 PRESET/POC

PRESET is buffered and combined optionally with POC to produce a RESET to the CPU when either input is low. PRESET resets the CPU, the PSYNC circuit, and the vector jump circuit.

POC is generated by U13 (555 timer) connected as an oscillator, except the discharge transistor (pin 7) is not connected. Therefore, upon application of power, the 555 turns on (pin 2 is below 1/3 Vcc) and the capacitor charges up. When the voltage on the capacitor reaches 2/3 Vcc (pin 6), the 555 output is turned off. The capacitor remains charged as long as power is applied. U24 inverts the 555 output to produce a POC. POC resets RUN/STOP flip-flop (so the CPU comes up running if the RUN/STOP switch is open), and is applied to the POC bus driver, and is optionally applied to U15C to reset the CPU and PSYNC circuit.

#### FIGURE 5.4.4 PRESET & POC

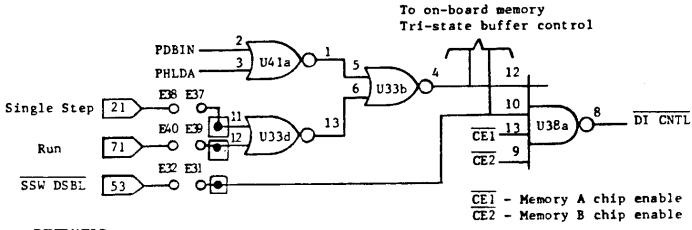

#### 5.4.5 SINGLE-STEP - RUN - SSW DSBL

These three signals, along with PDBIN, PHLDA, Memory A and B  $\overline{\text{CS}}$  (which are on-board signals), control the data coming into the CPU's bi-directional data bus. This is necessary to insure that the DATA-IN (DIØ thru DI7) and the on-board-memory tri-state drivers are not enabled when the CPU is trying to output data, and to allow front panel circuits to place instructions on the CPU's data bus without interference from other devices.

The RUN and SINGLE-STEP signals are similar, except that the RUN signal can also control the 2/4 MHz operation of the board. Both of these signals are generated by front panel circuits to control the DI bus and on-board memory

(when both are low, the DI bus and on-board memory are disabled). See Figure 5.4.5b for a truth table of this circuit operation. RUN, SINGLE-STEP, and SSW DSBL are optional signals on the CB2 because they are not part of the new IEEE standard bus. If not connected to the bus, they default to allow the CPU to operate normally.

FIGURE 5.4.5 SINGLE-STEP - RUN - SSW DSBL

#### a. SCHEMATIC

| PDBIN | PHLDA | SINGLE STEP | RUN | SSW DSBL | U4 la | PEEN | U33b | CE 1 | CE2 | U38a | DATA IN<br>BUS | ON-BOARD<br>MEMORY READ |

|-------|-------|-------------|-----|----------|-------|------|------|------|-----|------|----------------|-------------------------|

| 1     | X     | 1           | Χ   | 1        | 0     | 0    | 1    | 1    | 1   | 0    | Enabled        | Disabled                |

| 1     | X     | X           | 1   | 1        | 0     | 0    | 1    | 1    | 1   | 0    | Enabled        | Disabled                |

| X     | 1     | 1           | X   | 1        | 0     | 0    | 1    | 1    | 1   | 0    | Enabled        | Disabled                |

| X     | 1     | X           | 1   | 1        | 0     | 0    | 1    | 1    | 1   | 0    | Enabled        | Disabled                |

| 0     | 0     | X           | x   | Х        | 1     | X    | 0    | Х    | X   | 1    | Disabled       | Disabled                |

| х     | Х     | 0           | 0   | Х        | X     | 1    | 0    | X.   | Х   | 1    | Disabled       | Disabled                |

| X     | x     | X           | X   | 0        | Х     | Х    | X    | X.   | Х   | 1    | Disabled       | Disabled                |

| 1     | Х     | 1           | X I | 1        | ٥     | 0    | 1    | 0    | 1   | 1    | Disabled       | Enabled                 |

| 1     | Х     | X           | 1   | 1        | 0     | 0    | 1    | 0    | 1   | 1    | Disabled       | Enabled                 |

| х     | 1     | 1           | Х   | 1        | 0     | 0    | 1    | 0    | 1   | 1    | Disabled       | Enabled                 |

| х     | 1     | X           | 1   | 1        | 0     | 0    | 1    | 0    | 1   | 1    | Disabled       | Enabled                 |

| 1     | Х     | 1           | Х   | 1        | Q     | 0    | 1    | 1    | 0   | 1    | Disabled       | Enabled                 |

| 1     | X     | X           | 1   | 1        | 0     | 0    | 1    | 1    | 0   | 1    | Disabled       | Enabled                 |

| X     | 1     | 1           | Х   | 1        | 0     | 0    | i    | 1    | 0   | 1    | Disabled       | Enabled                 |

| x     | 1     | X           | 1   | 1        | 0     | 0    | 1    | 1    | 0   | 1    | Disabled       | Enabled                 |

#### b. TRUTH TABLE

SSW DSBL, when low, disables the DI bus tri-state drivers and the on-board memory tri-state drivers, so an external circuit (i.e., front panel) can put data on the CPU's internal data bus via the header W2.

#### 5.4.6 (STATUS, ADDR, C/C & DO) DSBL Signals

These signals, when low, disable the CPU's status, address, control, and data output tri-state drivers. These signals allow external devices to take control of the S-100 bus during DMA data transfers.

#### 5.5 Address Bus

The Z-80 has 16 address lines (65,536 possible memory locations and 256 I/O ports) that are not multiplexed with anything else. These address lines are buffered by 74LS244 octal bus drivers as shown in Figure 5.5. Two sets of buffers drive the high address lines (A8 thru A15) in order to duplicate the low address onto the high address bus during I/O operations (as does an 8080 CPU). IC's U1A & B, U3D, and U23A control the address bus buffers, as shown in the truth table of Figure 5.5b. The multiplexing of the low address onto the high address bus during I/O operations is optional, and is enabled by connecting E22 to E23 on the CB2.

#### 5.6 Data Bus

The data bus in the S-100 system consists of two 8-bit buses: a data-out bus (DO Ø thru 7) for data transfers from the CPU to external devices (i.e., memory and I/O cards), and a data-in bus (DI Ø thru 7) for data transfers from external devices to the CPU.

The data-out bus is driven by U49 (which buffers the CPU data lines from the heavy loads on the DO bus) and is normally enabled (since only the CPU drives this bus, except during DMA operations). DO DSBL controls tristating of this bus on the CB2.

The data-in bus is buffered by U50, which is tri-stated during CPU write operations, on-board memory operations, and certain front panel operations. Tri-state control of the data-in bus (U50) is discussed in Section 5.4.5 of this manual. The data-in bus lines are pulled up to +5 Vdc by RP9 (SIP) and R18, which helps to guarantee a logic 1 on the bus when nothing is driving it.

#### FIGURE 5.5 ADDRESS BUS

<sup>\*</sup> The high address bits during I/O in the Z-80 contain the accumulator contents during normal I/O and contain the B register bits during block transfer I/O (B register is the byte counter).

#### b. ADDRESS BUS I/O TIMING

Internally, the CPU data bus is bi-directional and has a pull-up resistor network (RP8 and R17) to help speed up the transitions from logic 0 to logic 1 on the internal bus lines. Also, a header socket (W2) is provided. This allows front panel circuits to drive and sense the CPU data bus directly.

#### 5.7 Extended Address Port

This circuit is an output port at address GFEH. U20d decode the address OFEH and put a logic 0 on U36 & 40 pin 10 as one write enable. TORQ from the Z-80 provides the other write enable to U36 & 40 at pin 9. The data is clocked into U36 & 40 (pin 7) by  $\overline{WR}$ . latches U36 & 40 are reset when the CPU is reset, so the address will be 000000H. The tri-state output enable is controlled by U1, as are the low address buffers.

The port output goes to a header socket (W1) so that it can be used as an output port, or can be used as extended address bits (if W1 is strapped straight across).

IORO WR A16 DØ 15 13 A17 16 D1 U36 74173 A18 15 D2 13 14 A19 59 **D**3 Z-80 Bidirectional 14 A20 61 Data Bus 3 **D4** E 13 A21 62 **D5** U40 74173 10 5 12 A22 63 **D6** 6 A23 64 **D7** Reset (from U39c pin 10) -ADDR DSBL (from Ul6 pin 4) 12 ΑØ 11 Address

FIGURE 5.7 EXTENDED ADDRESS PORT

#### 5.8 On-Board Memory

There are two on-board-memory sockets with independent address circuits. Each socket can accept either 2716, 2732, or TMS 4016 memory chips.

Data is transferred to and from the memories through the tri-state buffers U18 and U19. U18, U19, and the output enable  $(\overline{\text{OE}})$  of the memories are controlled by U2A & B. When one of the memories is selected (U3C, pin 8=logic 1), and  $\overline{\text{SSW DSBL}}$  is high, and DBIN is high, then U2B outputs a logic 0 to enable data onto the CPU data bus. When any one of the signals to U2B is low, the U18 is tristated and U19 is turned on. Because the memories are also tri-stated, U19 and the memories are not in conflict.

The chip select  $(\overline{CS})$  circuit is identical for both memories. Therefore, memory A will be described and the appropriate circuit elements for the B memory will be indicated in parentheses ().

U9 provides buffering and address inversion for the upper 6 address bits (upper 5 bits for 4K memories) to the address comparator circuit. The address for memory A is selected by dip switch SC (SD) and is compared by U8 & U14D (U4 & U14A). When the address bits and the dip switch settings are in opposite logic states, the comparator outputs will all be a logic 1. The outputs are open collector and pulled up by a resistor. Therefore, if any XOR gate has matching inputs it will be a logic 0 to U3 pin 2 (U3 pin 5). When U3A (U3B) receives a logic 1 from the comparator and MREQ from inverter U14C, then memory A (B) is selected. The chip select  $(\overline{CS})$  for memory A only is enabled by either Vector Jump enable or by the output of U3A. (A jump instruction should be the first three addresses of Memory A if a POC or RESET is strapped for a vector jump.) U3C produces a logic 1 (MSEL) when either memory is selected.

Pin 21 on the memories is a multi-purpose pin. It is an address (A11) input for 2732. It is WR input for TMS 4016 (or equivalent 2K RAM). It is the Vpp pin on the 2716, which is held at the +5 Vdc during normal operation. The switches of SE select which type of input (A11, WR, or +5Vdc) each memory will receive.

FIGURE 5.8 ON-BOARD MEMORY

#### 5.9 Vector Jump

A vector jump is initiated by  $\overline{POC}$  and/or  $\overline{PRESET}$  when jumpers E18 & E19 and/or E24 & E25 respectively are installed. U23B & C form an AND gate so that when either input is low, U22A & B are both set. If no vector jump is desired, the E18, E19, E24 & E25 should be left open and E16 & E17 should be connected, so that U22A & B are reset by  $\overline{POC}$ .

U22A & B are connected to form a two-bit shift register that will shift logic 0's across when clocked. M1 is the clock signal for the shift register. Therefore, U22B is clocked to logic 0 on the first M1, which is the vector jump Op-Code Fetch. U22A is clocked to a logic Ø on the second M1, which releases memory A and allows the computer to operate normally. In this way, one instruction at the beginning of memory A is executed (which should be a jump instruction).

FIGURE 5.9 VECTOR JUMP

#### a. SCHEMATIC

6.0 TROUBLESHOOTING HINTS

This section assumes the user has some basic knowledge of logic circuits and has read the theory of operation section of this manual. It is also assumed that the user has or has access to a voltmeter and a logic probe or an oscilloscope.

- 6.1 Verify that all IC's are in the correct sockets, and that none of the IC pins are bent under, and the IC is installed with the correct orientation.

- 6.2 Verify that each regulator is putting out +5 volts.

- 6.3 Verify that all necessary options have been connected properly.

- 6.4 Check for proper settings of DIP switches.

- 6.5 Inspect the back side of the board for any solder bridges. Run a small sharp knife blade between traces that may appear suspicious. A magnifying glass is recommended for this inspection.